本人发现还有许多朋友在寻找如何仿真蜂鸟E203的方法,并且目前论坛内还没出现过一代蜂鸟E203(基于hbirdkit和nucleikit)仿真教程,由于本人使用的板子便是hbirdkit,因此特来分享一代E203的vivado调试方法(windows/linux皆可)。 比赛小队名:强强联合队。报名编号:CICC1316

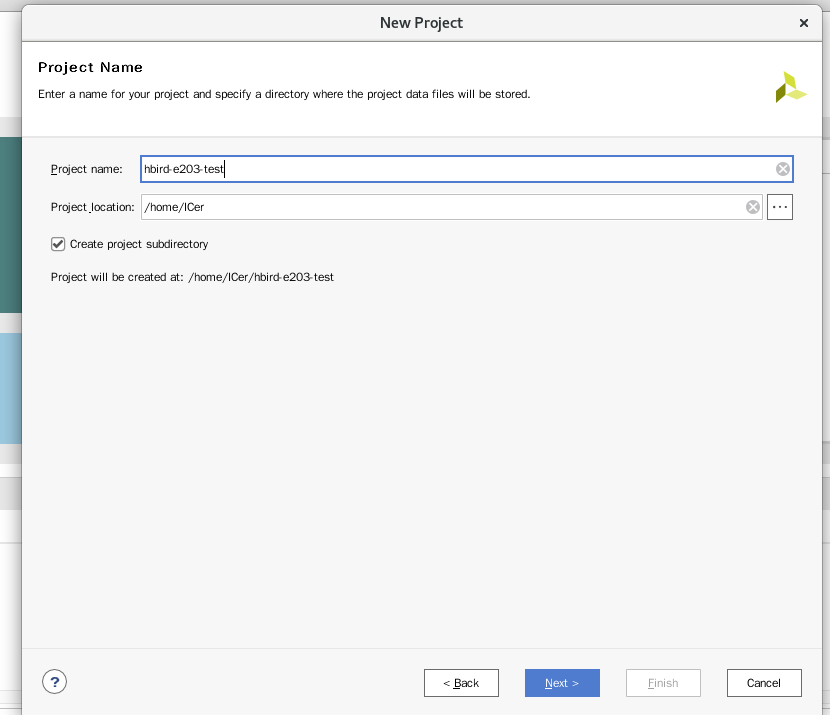

1.新建vivado项目

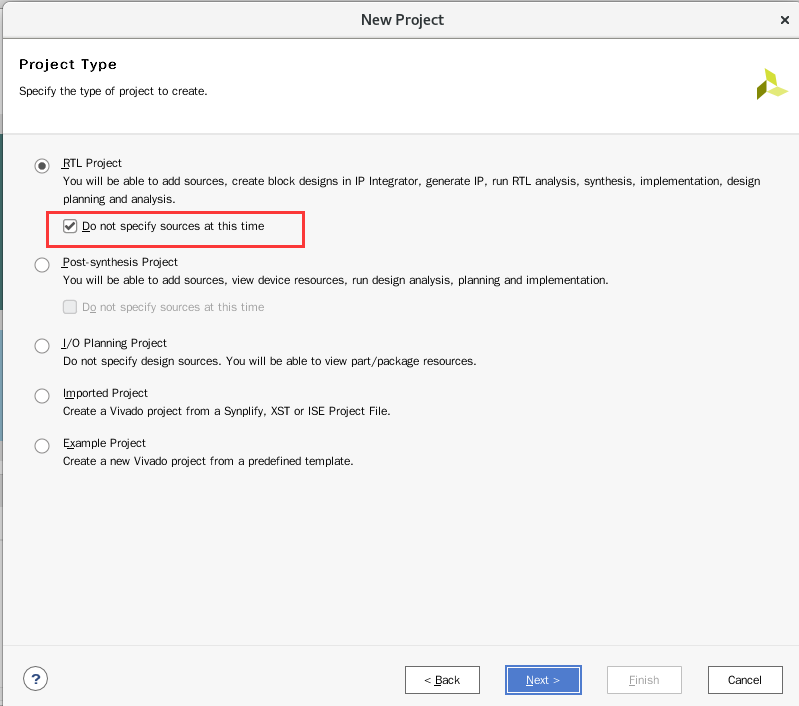

此处注意勾选Do not specify sources at this time (此时不指定源)

此处注意勾选Do not specify sources at this time (此时不指定源)

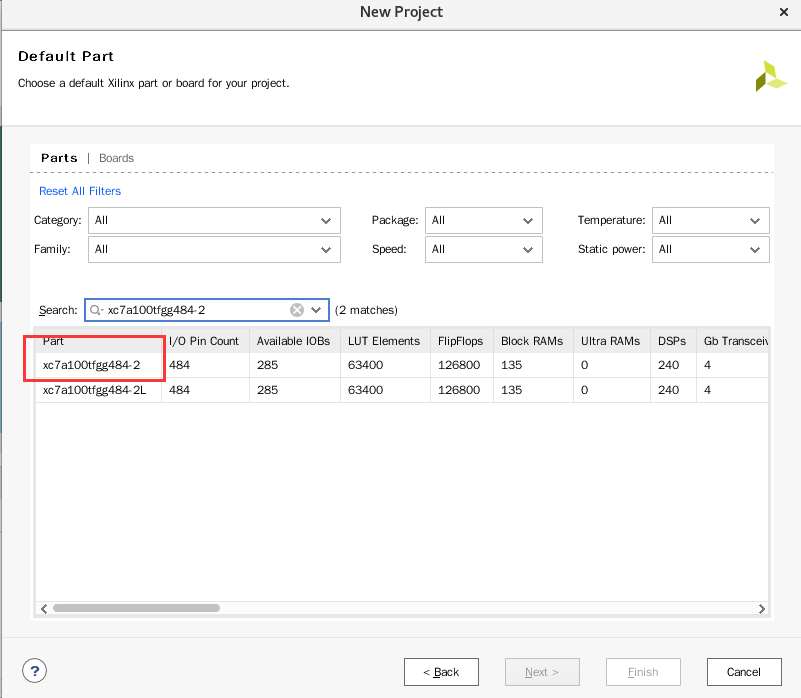

本人使用的是较早的蜂鸟评估板,型号如图所示,大家要根据自己型号选择

本人使用的是较早的蜂鸟评估板,型号如图所示,大家要根据自己型号选择

随后点击next,finish便会出现项目界面:

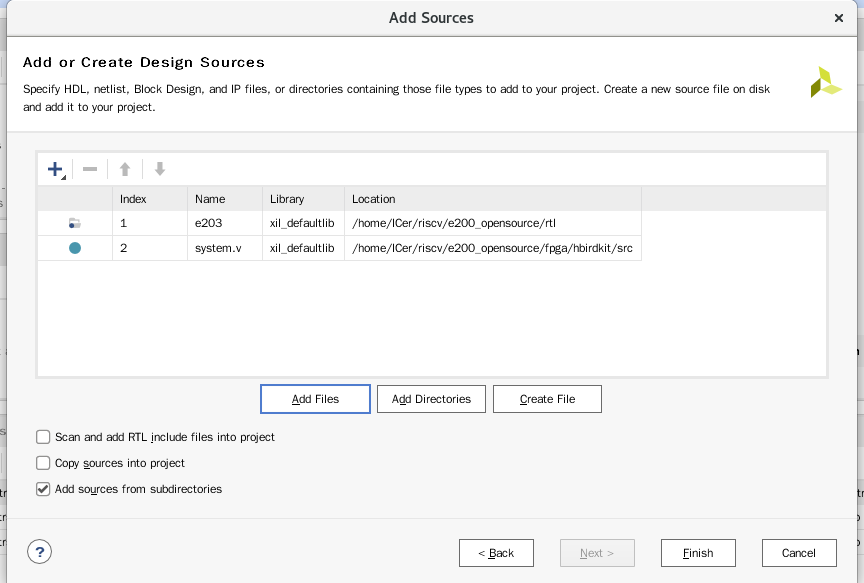

2.加入E203的RTL代码和system.v(顶层文件)文件

加入e200_opensource/rtl/e203文件夹以及e200_opensource/fpga/hbirdkit/src/system.v(原本是system.org,将后缀org改成v)

点击finish,RTL添加完毕

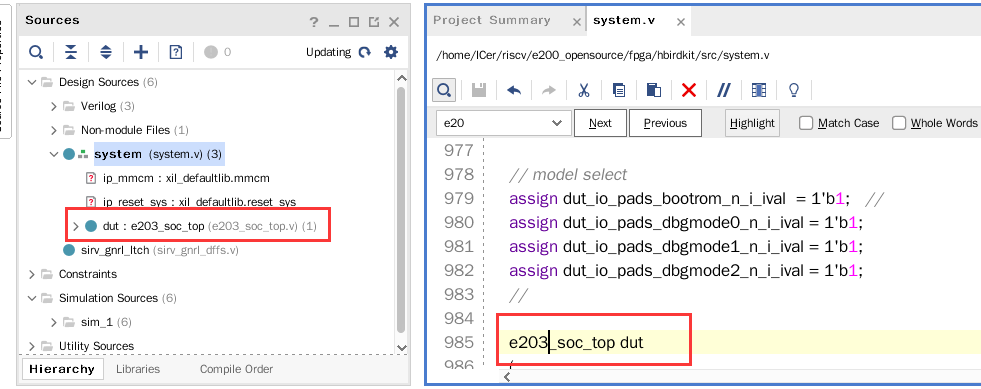

此时顶层文件下有3个问号,先打开system.v,search e200,将e200改成e203,最下面那个问号会消失

此时顶层文件下有3个问号,先打开system.v,search e200,将e200改成e203,最下面那个问号会消失

3.添加IP,根据e200_opensouce/fpga/hbirdkit/script下的ip.tcl文件的描述,可以得到需要添加的两个IP的内容

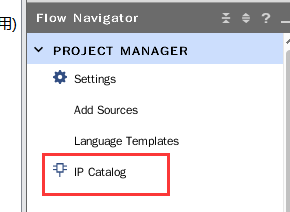

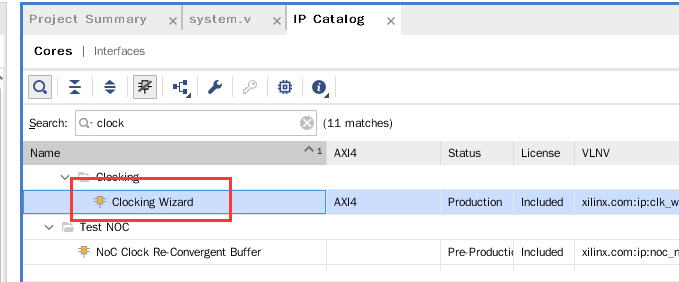

选择IP Catalog

选择IP Catalog

search clock 往下面找

search clock 往下面找

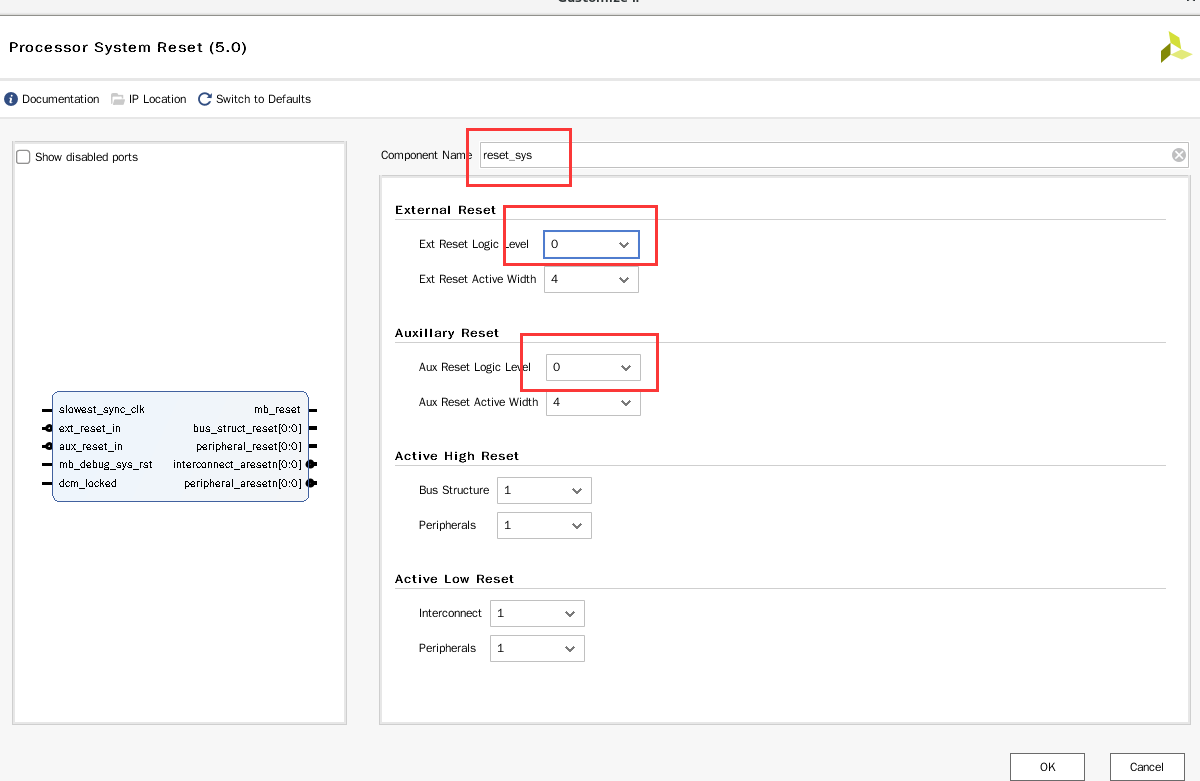

双击打开Processor System Reset 添加复位IP核

双击打开Processor System Reset 添加复位IP核

进行如图修改,后确认。

进行如图修改,后确认。

点击generate

点击generate

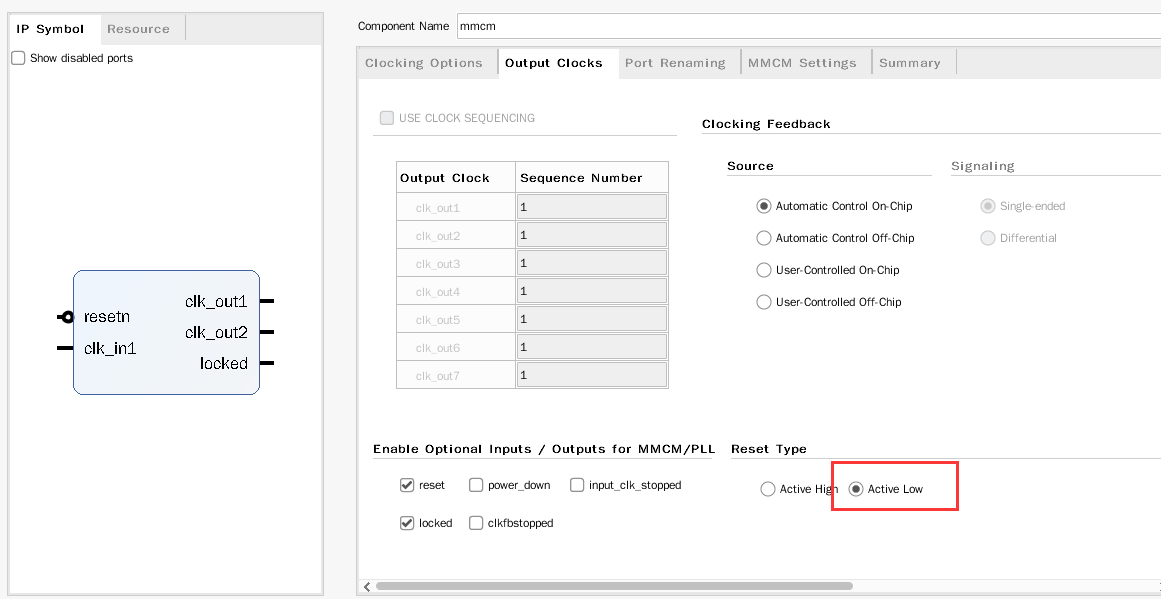

同理,找到时钟IP核:

先记得修改名字

先记得修改名字

改输出时钟值

改输出时钟值

再设置为低电平复位,随后 OK generate即可

再设置为低电平复位,随后 OK generate即可

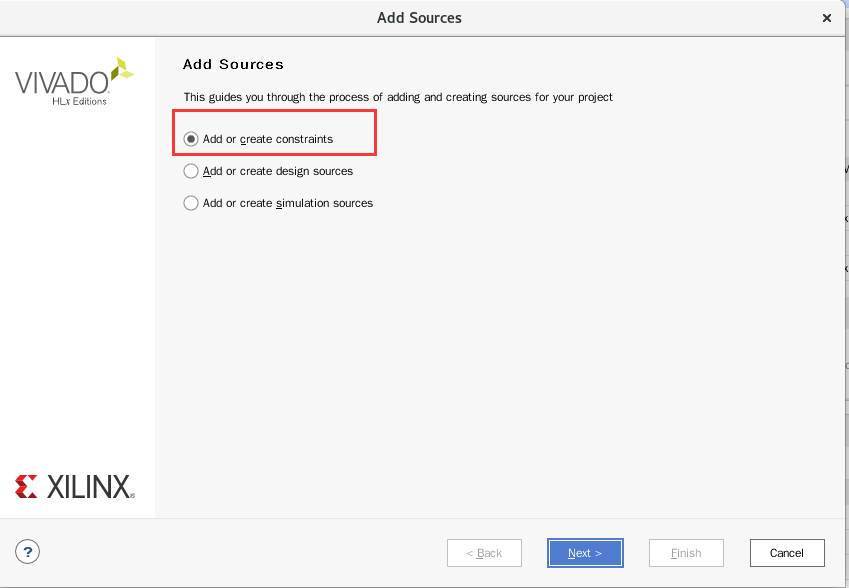

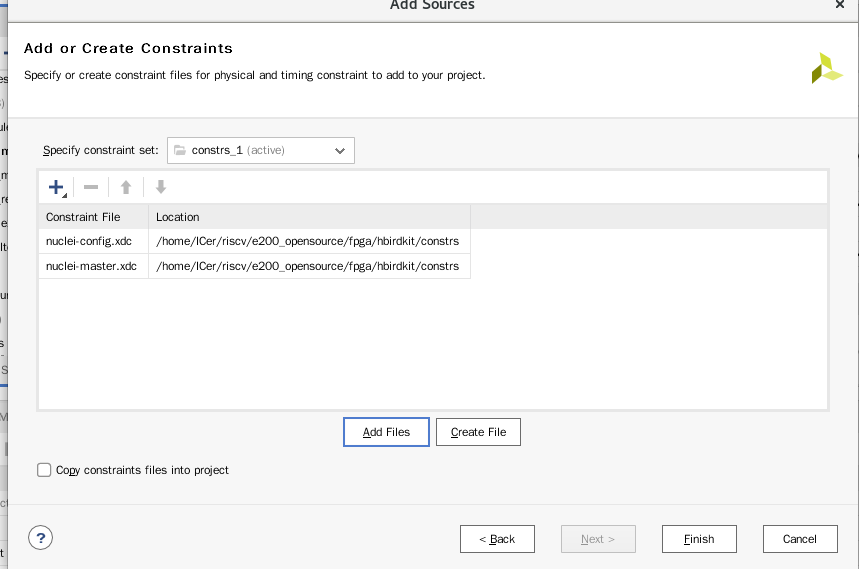

4. 添加约束文件

约束文件位于e200_opensource/fpga/hbirdkit/constrs

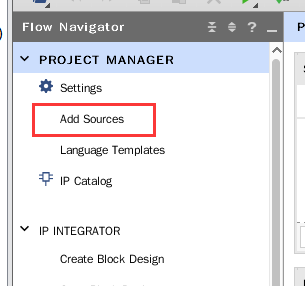

左边Add sources:

两个文件都添加

两个文件都添加

约束文件添加完毕

约束文件添加完毕

5.添加测试文件tb

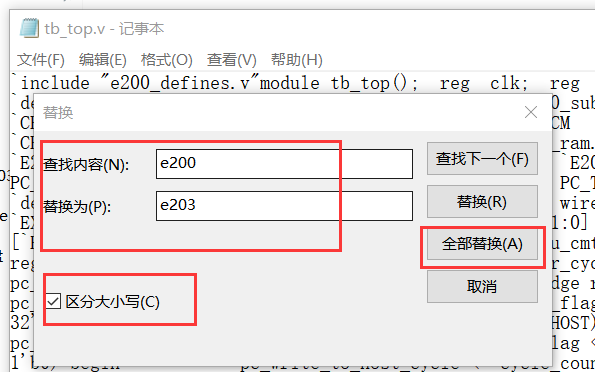

tb文件位于e200_opensource/tb里的tb_top.v 先用记事本打开

将e200全部替换为e203 注意勾选区分大小写

将e200全部替换为e203 注意勾选区分大小写

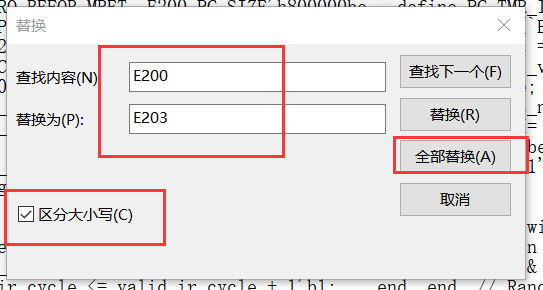

同理,将E200全部替换为E203

同理,将E200全部替换为E203

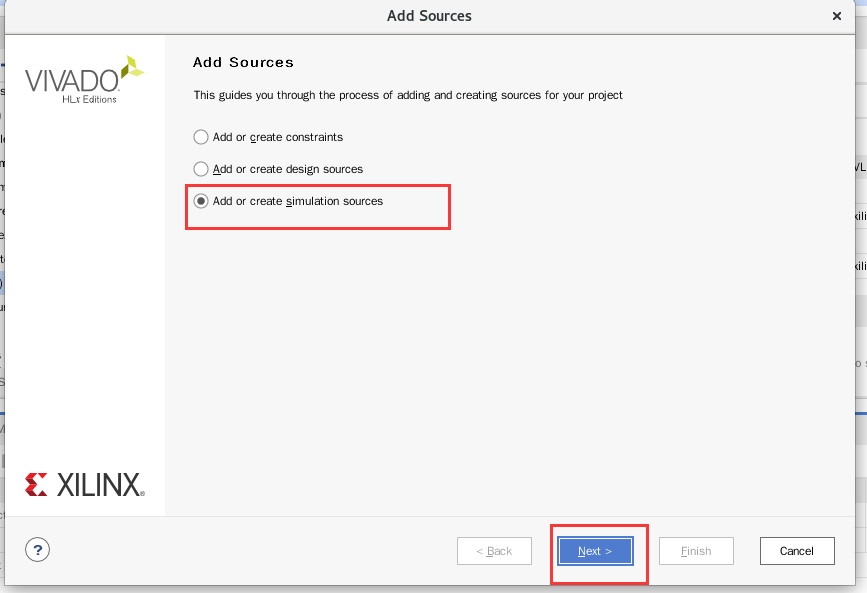

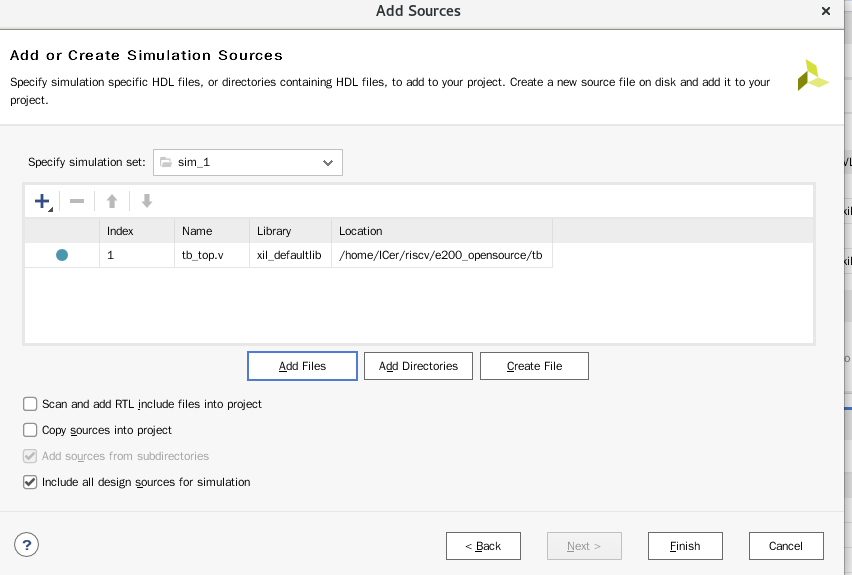

修改完毕后即可将tb添加到源文件中

此时,测试文件也添加完毕

此时,测试文件也添加完毕

6.最后的修整

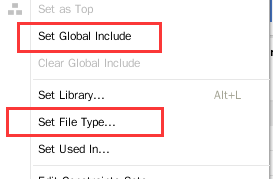

将e203_defines.v设置为global include,再将type设置为verilog header

将e203_defines.v设置为global include,再将type设置为verilog header

否则会报错

否则会报错

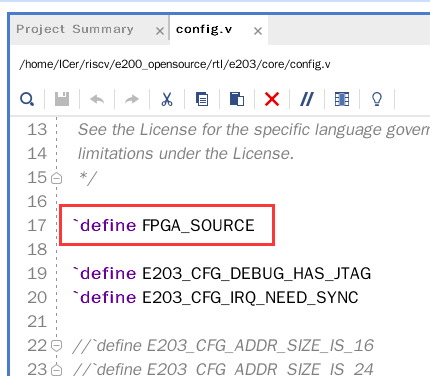

在config.v中添加这一句话,以便后续的仿真

在config.v中添加这一句话,以便后续的仿真

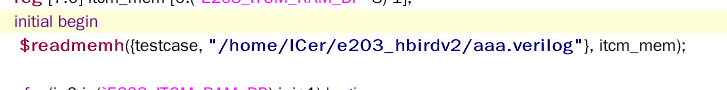

在tb_top.v里可以添加verilog文件路径,以便可以对编译后的verilog文件进行仿真

在tb_top.v里可以添加verilog文件路径,以便可以对编译后的verilog文件进行仿真

右键将tb_top.v设置为Top

右键将tb_top.v设置为Top

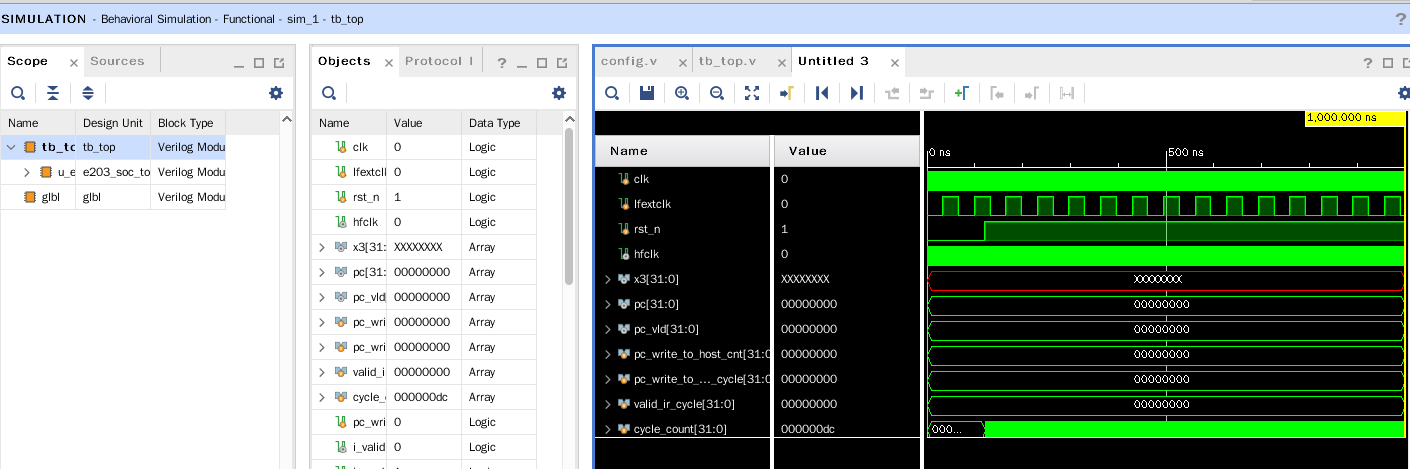

最后,点击run simulation 进行 行为级仿真

进行 行为级仿真

得到最后的仿真结果如图所示

本文参考论坛内另外两篇文章:

[1] 在Windows环境下用Vivado调试E203 作者:leon

[2] 【分享】技术分享--利用NucleiStudio IDE和vivado进行软硬件联合仿真 作者:Jue

不知为何无法复制网址,只能用署名的方式感谢原作者提供的思路。

本文也可以作为新手学习vivado的教程。

如果文章还有什么纰漏,希望大家指出,非常感谢。

2021.4.14 修改 文章步骤没有问题, 不加system.v 单单加入e203的rtl代码也可以使用

附赠一个hbirdv2基于Nuclei Studio 的 Nice Demo 协处理器仿真生成的verilog文件可直接加入到tb里进行软硬协同仿真,不过一代蜂鸟里面没有添加NICE协处理器接口的支持 。

下载附件:下载:test

仿真结果:

需要先让仿真跑一会才会出现如图结果。