1.简述

首先感谢芯来开源了蜂鸟E203 risc-v处理器,提供了比较完整的工程环境、配套的软硬件。但是配套的FPGA板卡实在太贵,对于自费学习的来说是不小的学习成本,而且我也认为完备环境在一定程度上为我们学习提供便利,但反过来说你会忽略很多基本的细节,这部分恰好别人做好的,很多人会陷入一个学习误区,使用命令run一下,再将工程烧写到配套的FPGA跑一跑就觉得学得差不多了,好像没有任何问题,所以我喜欢折腾,因为折腾迫使我不断去解决问题,在解决问题的过程中会思考很多细节,而且印象更加深刻。当然这是我个人的学习方法。

如果手上有Xilinx的 FPGA板卡,可以一起学习一下怎么将e203移植到自己的板卡上。

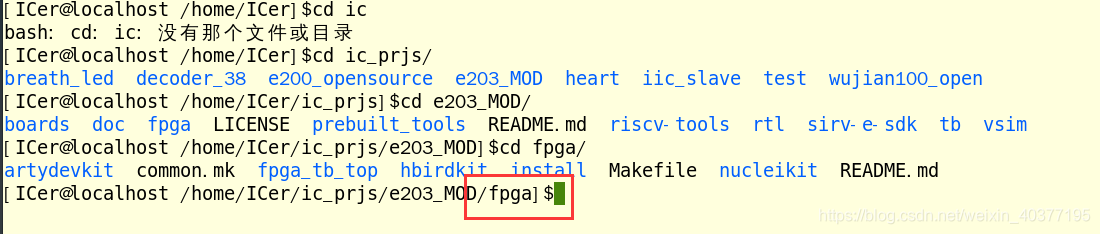

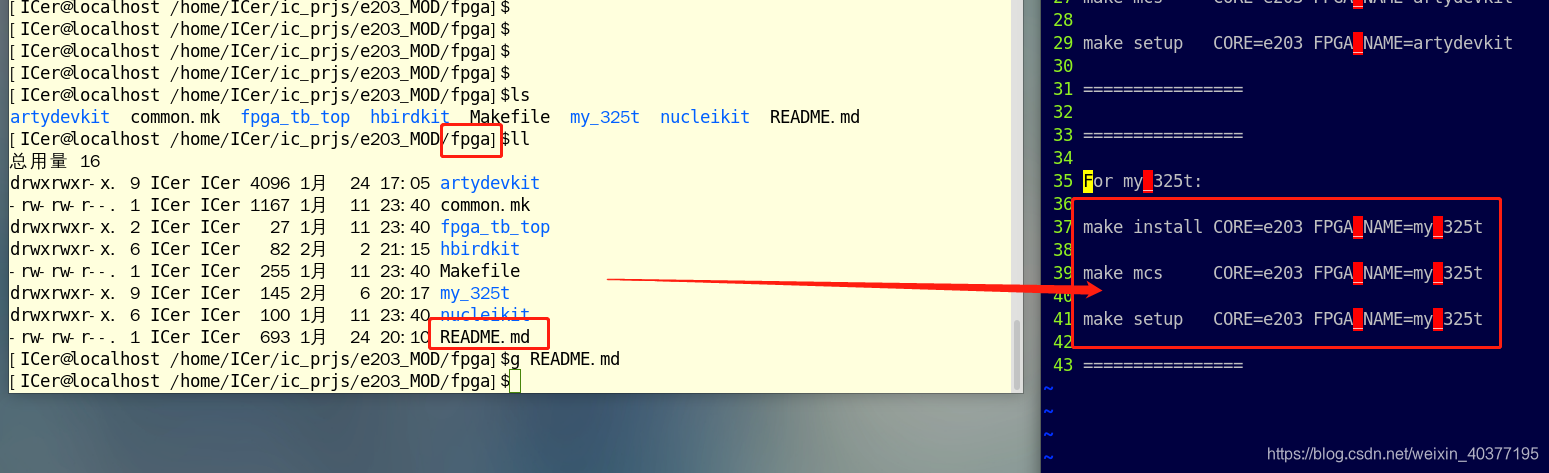

进入到FPGA目录下;

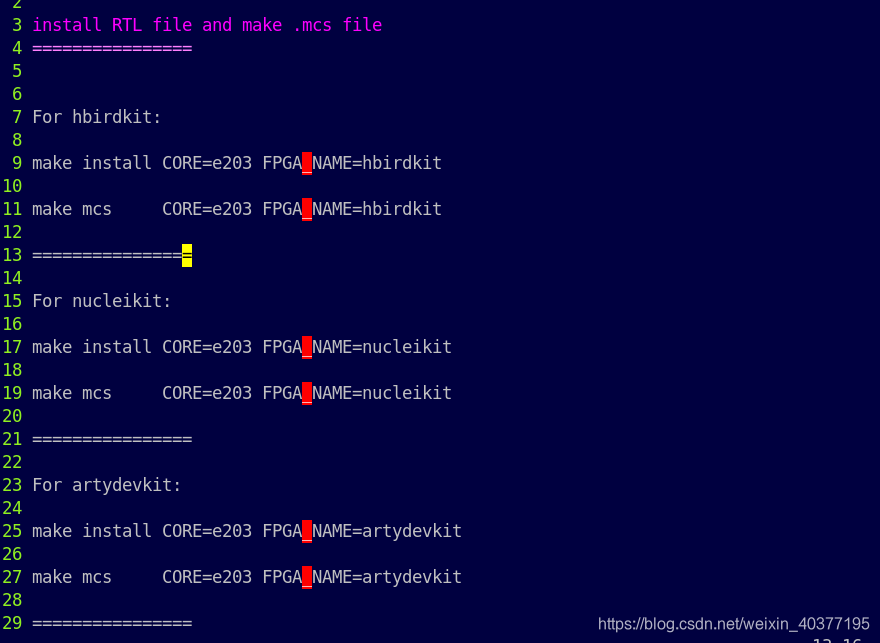

gvim打开“README.md”文件,下面就是FPGA综合的命令。

这里以最后一个:artydevkit为例,这个是Digilent的FPGA板卡,我们可以参考这个工程修改成我们的FPGA。依次执行以下命令。第二个直接使用“setup”可以打开vivado的gui查看整个工程。

make install CORE=e203 FPGA_NAME=artydevkit

make setup CORE=e203 FPGA_NAME=artydevkit

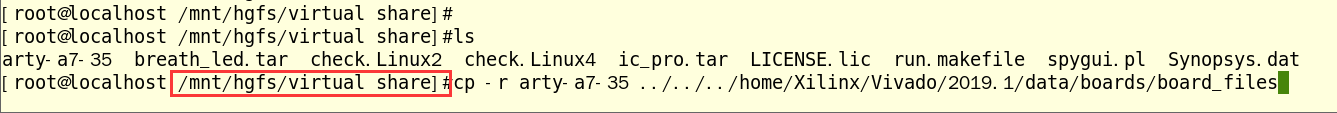

cp -r arty-a7-35 ../../../home/Xilinx/Vivado/2019.1/data/boards/board_files/

回到e203工程的FPGA目录下,重新运行命令,成功启动vivado并加载整个工程;

1)复制环境

复制一份artydevkit的环境来修改,新的名字可以自己取,我这里叫“my_325t”;

为了方便操作,我们先在README文件加入我们板卡的操作命令,以后可以直接复制这些命令,不用手动输入。

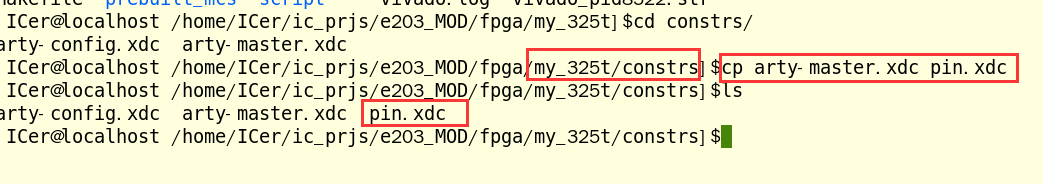

进入到“my_325t”目录下的constrs,复制一份约束文件,根据自己板卡资源修改。如果板卡的没有约束文件中的外设,可以将其注释掉,比如我将RGB LED和GPIO注释掉。当然后面就需要修改FPGA顶层文件,这个后面会说。但是板卡有相应外设,自己修改管脚号就可以了

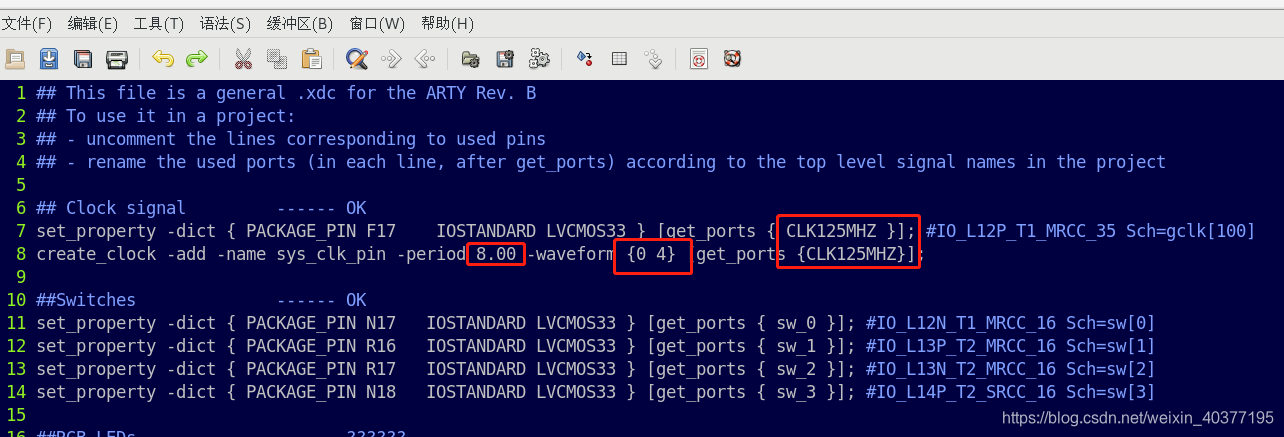

其次就是时钟,我的板卡只有125M单端时钟,所以约束的修改如下图所示,为了避免混淆直接将时钟信号名都改了。

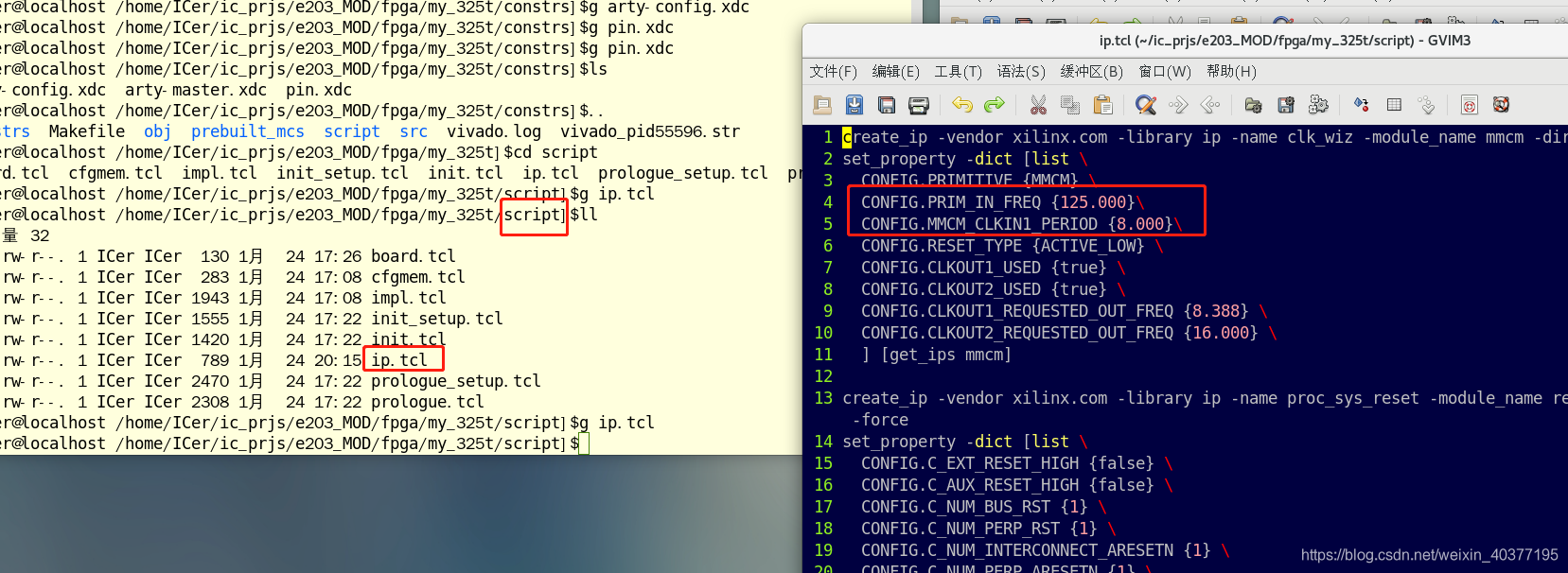

这里需要修改脚本,如图修改ip.tcl脚本,这个生成vivado的IP,添加如下两行脚本,配置clocking wizard IP输入时钟的属性。

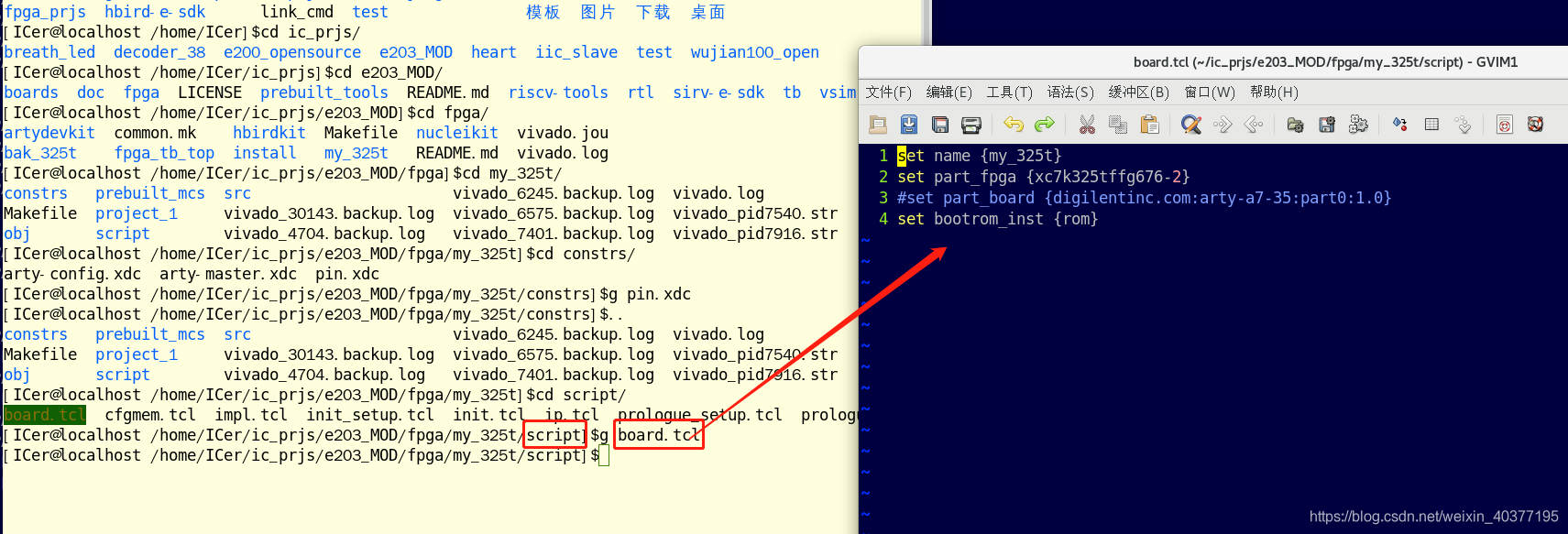

先修改board.tcl脚本,如图,主要修改第二行FPGA型号,注释掉第三行。

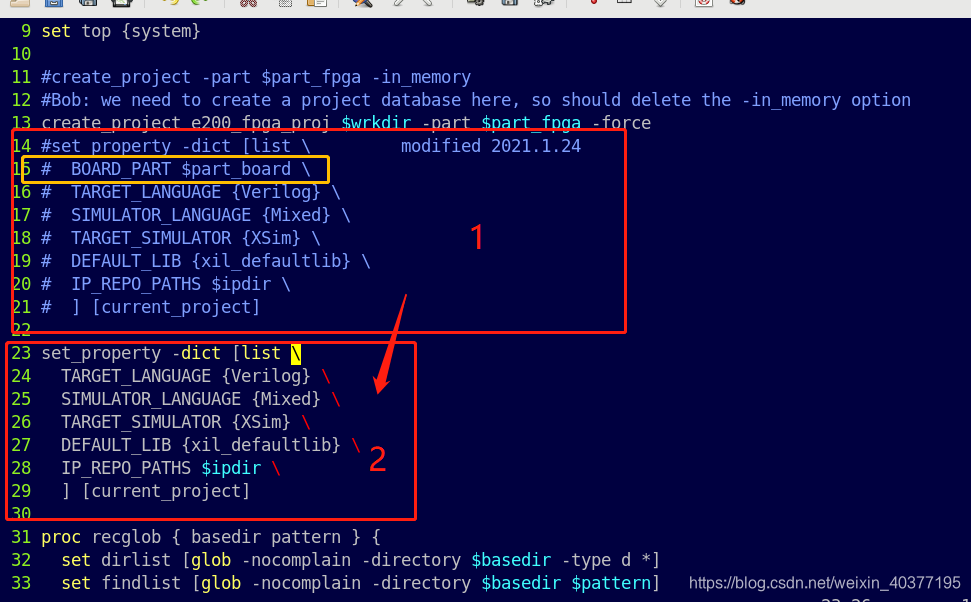

其他脚本也需要修改,如果有board相关的全部注释掉,如图,1为之前内容,将其注释备份,复制一个将board去掉。

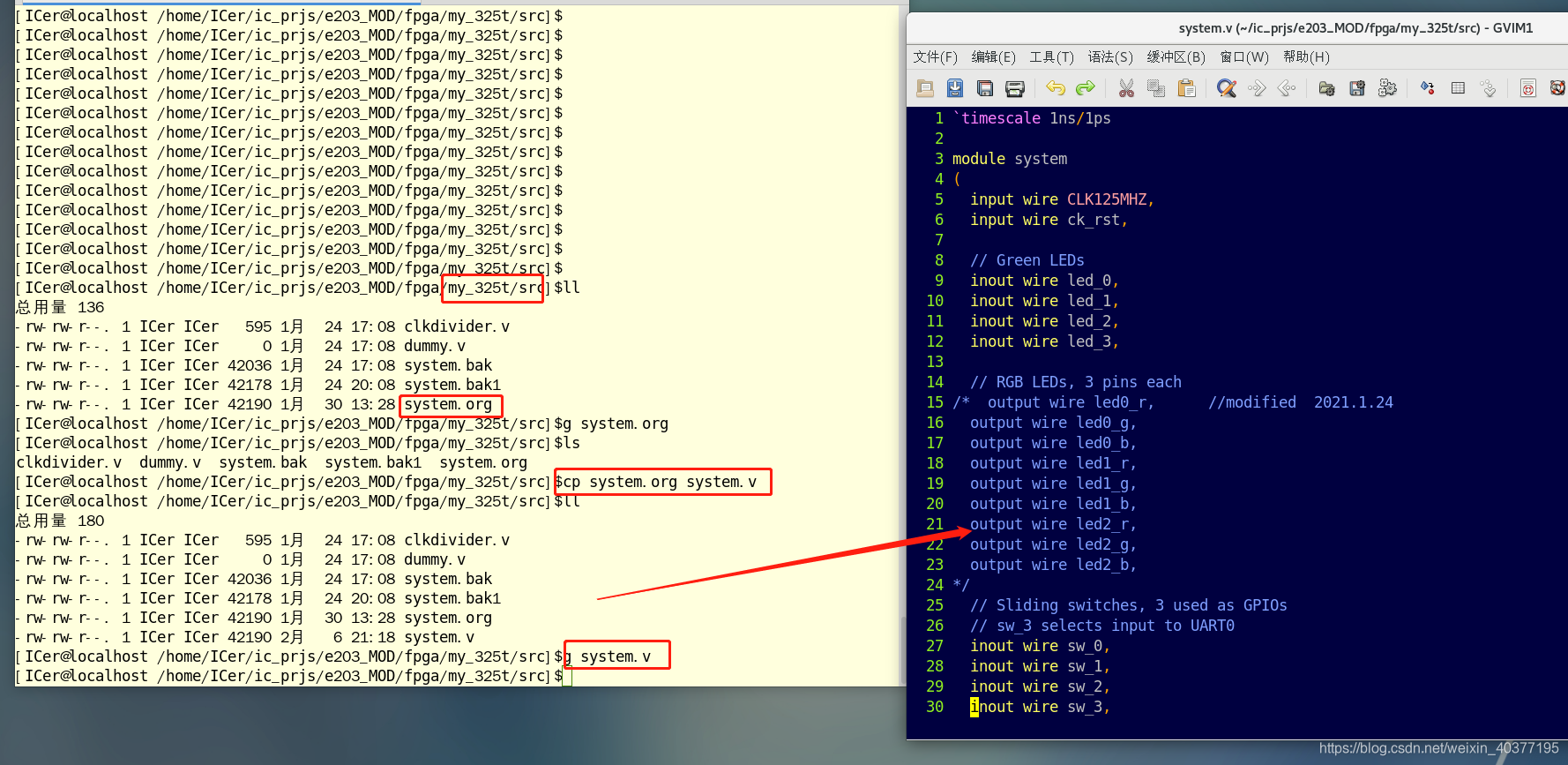

进入如图目录,有个system.org,这个是E203 的FPGA顶层,前面注释很多没有用外设,也修改了时钟信号名,所以需要大改这个文件。

gvim不会识别.org的文件,所以这里复制 “system.org” 为 “system.v”,然后使用gvim打开“system.v”进行修改,就能语法高亮。修改好后记得将文件改为.org结尾文件,不然使用install命令进行cp时找不到这个文件。

首先将之前100M时钟信号名全部替换为125M的。然后将约束文件注释的输入输出端口也注释掉。

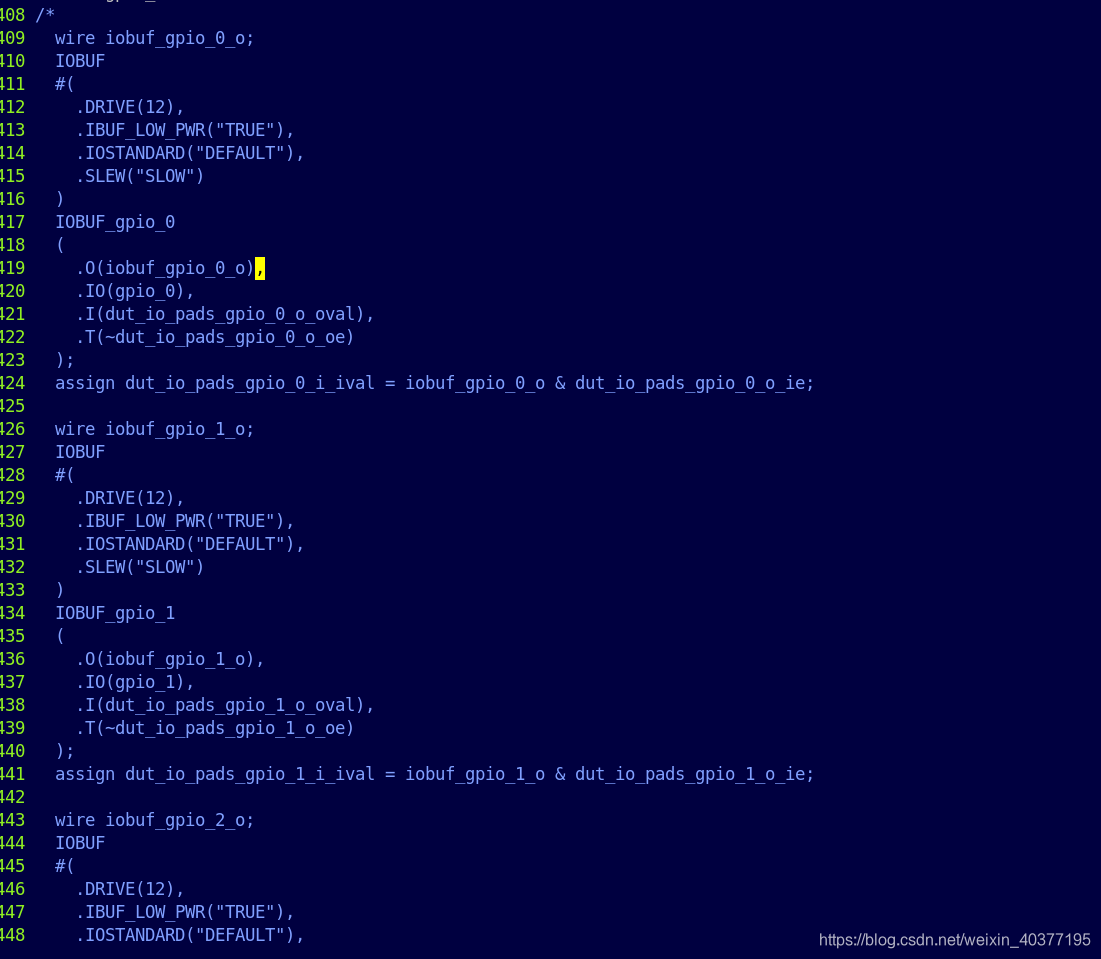

这些驱动外设的信号是通过IOBUF驱动的,所以注释掉的端口,对应的IOBUF也注释掉,不然会报错。如图是我注释的信号,具体注释那些你可以先进行综合,根据综合出来的错误信息将gpio iobuf注释掉。

使用以下命令,先进行install,然后setup启动Vivado Gui,自动加载e203源文件和约束文件。

make install CORE=e203 FPGA_NAME=my_325t

make setup CORE=e203 FPGA_NAME=my_325t

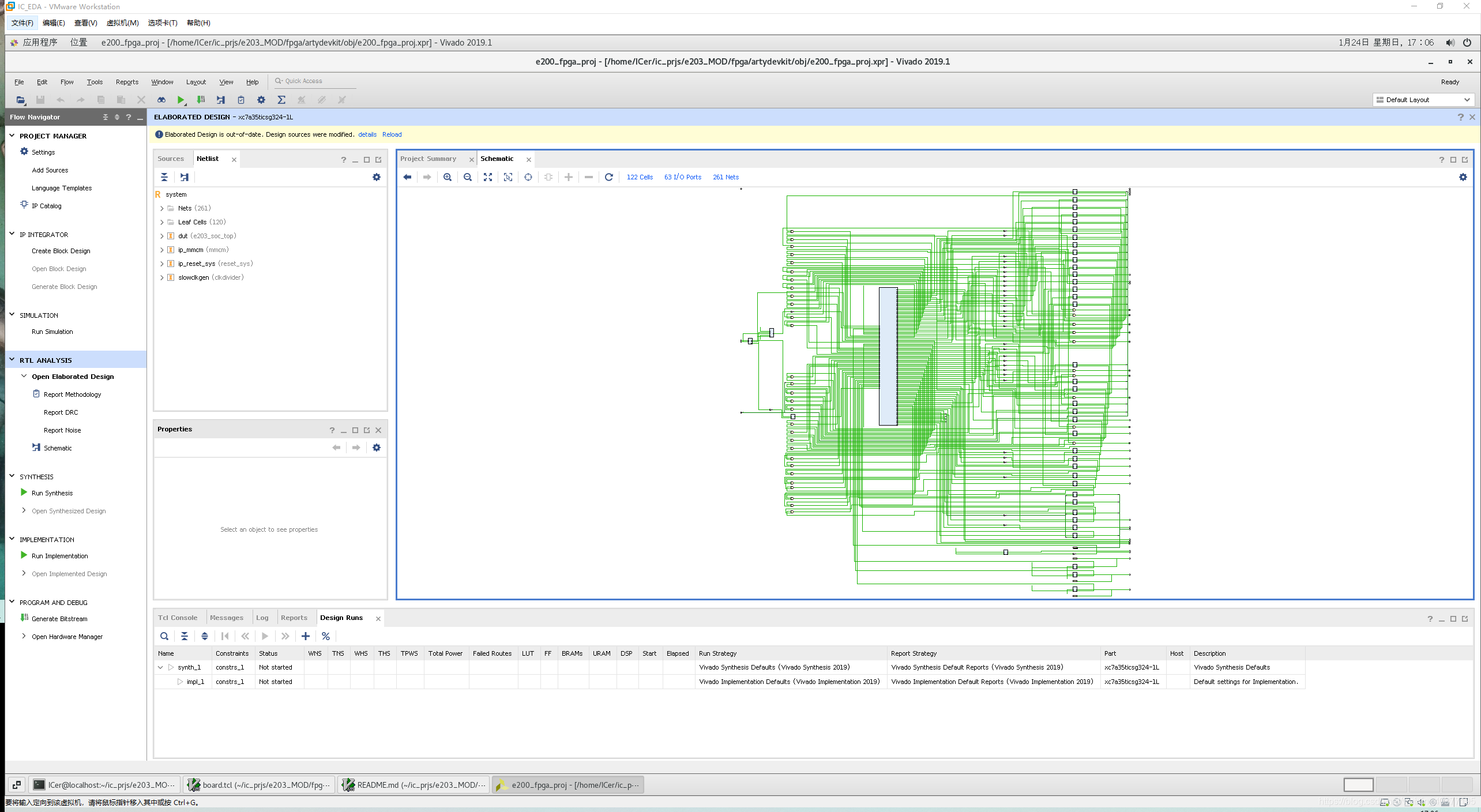

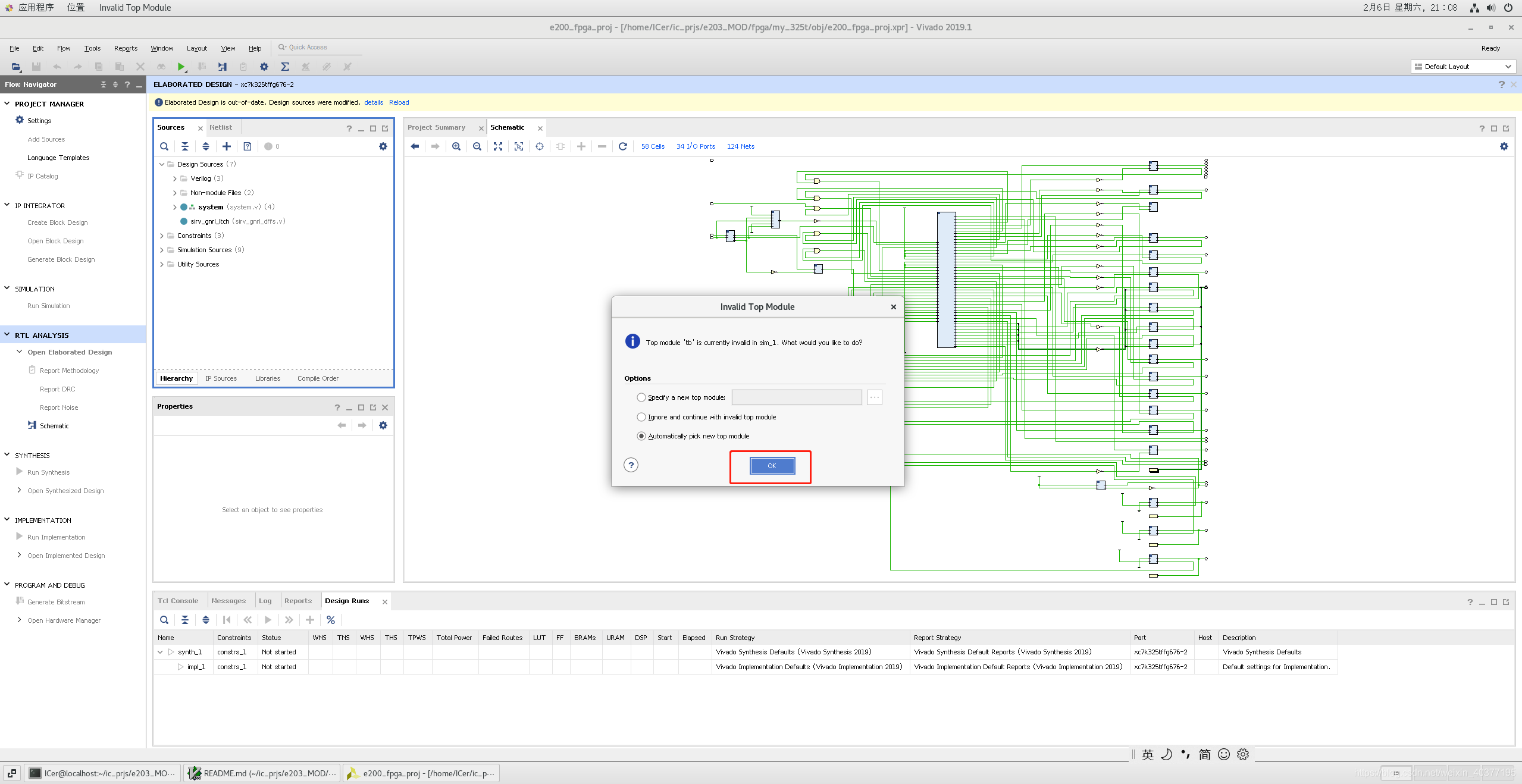

启动vivado后,可以看到如下界面,说明启动成功。这里点下ok,等待一会儿。

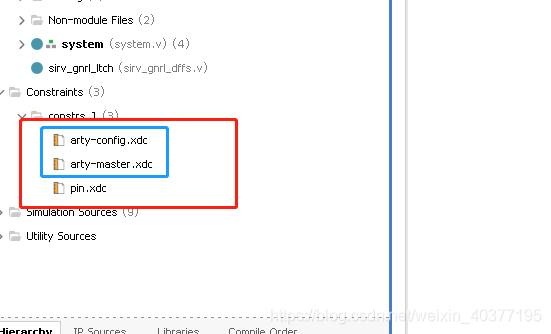

vivado加载所有的约束文件,这里需要将旧的文件remove掉,也就是蓝框的两个文件。

进行综合时,如果提示jtag tck的iobuf错误,建议在约束文件中添加如下约束:

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets IOBUF_jtag_TCK/O]

烧写到FPGA板卡后,第二个LED应该会亮。固化根据自己板卡操作一下就行,这里就不说了。

修改FPGA环境比较复杂,但是经过不懈的努力最终还是综合成功。这部分基于我之前分享的EDA环境进行的,公众号后台回复:EDA虚拟机可以获得完整EDA环境(虚拟机)。这个修改好的E203工程我也上传到gitee,传送门:蜂鸟修改板:E203_mod。