一、自制乘法器

为提高运算效率我们组结合了查找表乘法器和并行乘法器的思路设计了自己的乘法器IP,主体思路是将32位的输入数据分解为16个2位的数据相乘再错位相加。

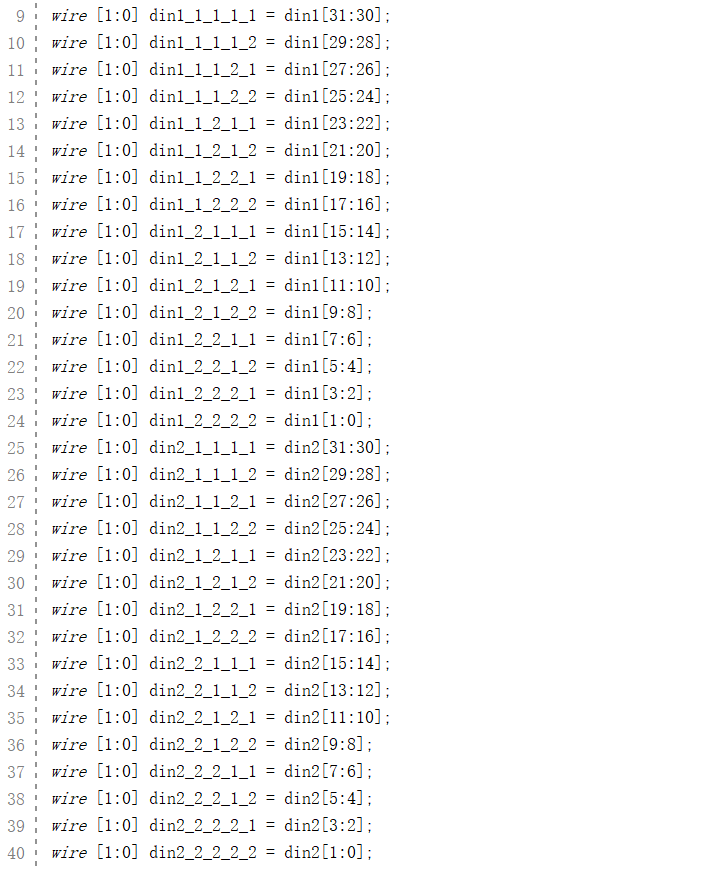

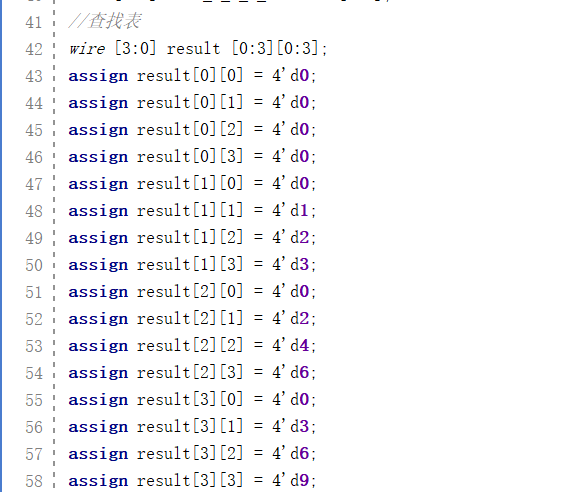

2位数据相乘运算采用了查找表的形式,直接在IP内定义一个4*4的wire型数组并对其赋初值。

将各级乘法结果叠加时要注意每一个结果对应的位数,每一个二位乘法器对应的结果最大为4'd9,而相邻位所得的乘法结果之间的位差是2位,所以叠加时会有2位的重叠,这里我采用了错位拼接最后再整体相加的方式规避了重叠的问题,即间隔4位的乘法结果可以直接拼接,求和时不会有对应位的加法运算。

比如以下代码,将din1的[31:30]位与din2的[31:30]位、[27:26]位的乘法结果可以直接拼接无需加法运算,din1的[31:30]位与din2的[29:28]位、[25:24]位的乘法结果也可以直接拼接无需加法运算,再将交错的拼接结果进行加法运算即可。

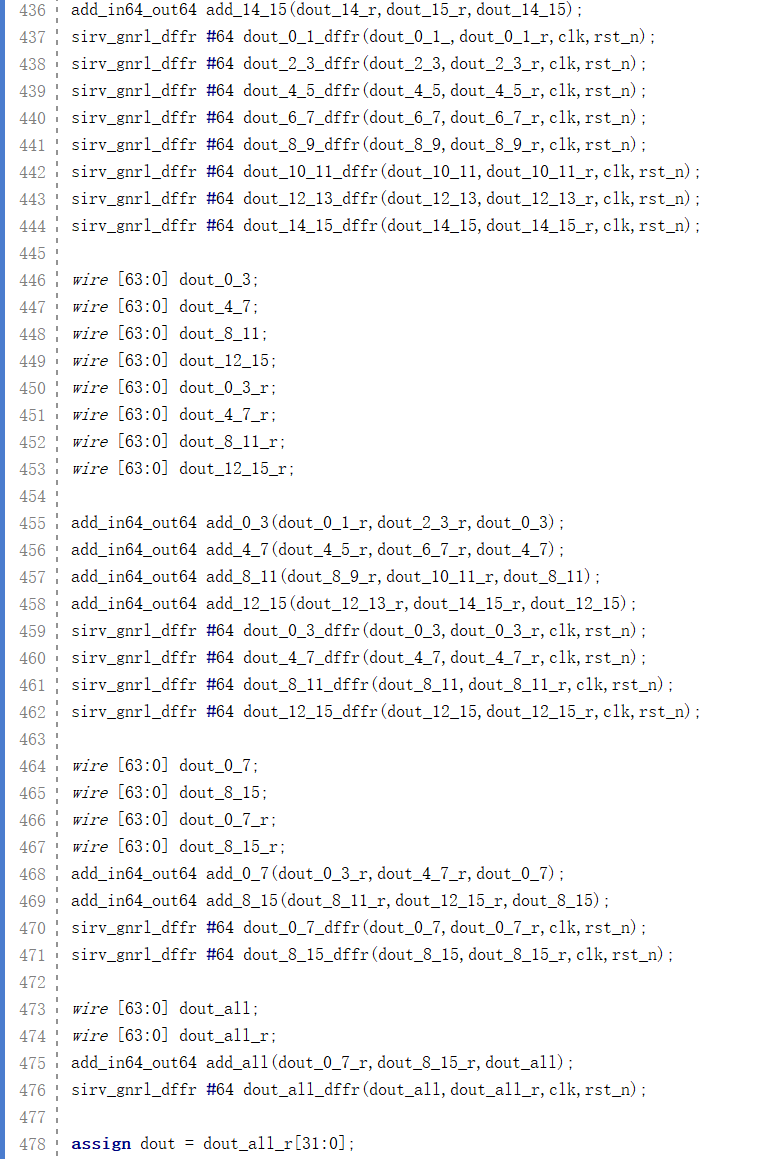

拼接运算几乎是不消耗时间的,而加法运算会有一定的时延,所以每进行一层加法运算都会插入一层寄存器,所需的加法运算是拼接后的加法运算以及得到的加法结果之间的累加,最后流水线级数是6级,改变信号的位宽只需微调内部逻辑,最终会改变流水线的级数。

二、自制加法器

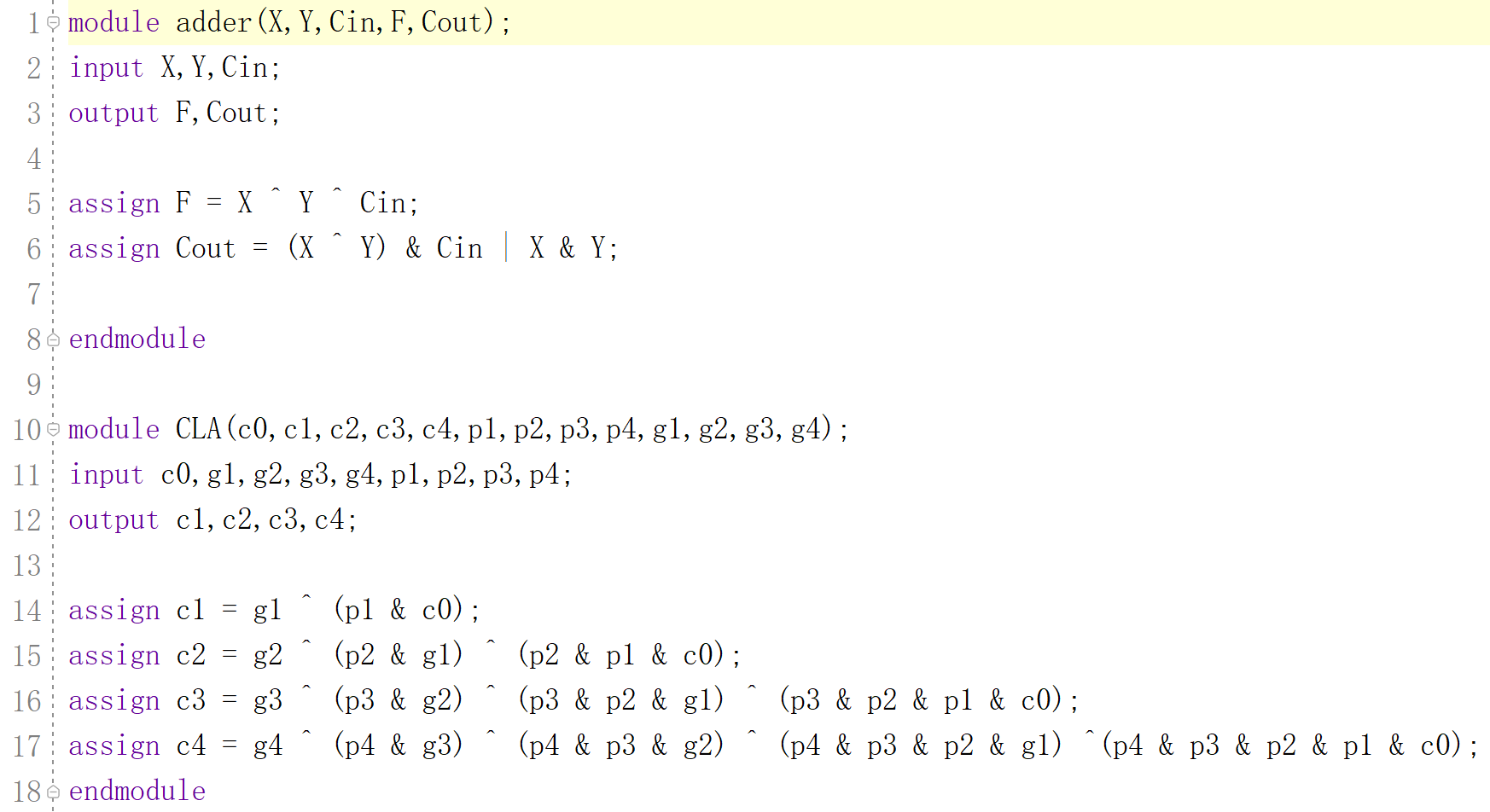

自制加法器使用的是简单的并行加法器,我以1位的并行加法器位初始单元例化出4位、16位、32位并行加法器,以32位加法器实现串行64位加法器再用于乘法器中,以下是1位并行加法器源码。

PS.在组合加法器和乘法器实现乘加器功能时要注意乘法器的流水线结构,即对输入的加数信号做等同于乘法器流水线级数的信号延时。

可以在变量前插入(*keep="true"*)时为了避免综合过程信号被优化,这样可以在综合报告中看到每一个模块的LUT资源利用率。