报名编号:CICC1355

团队名称:有点难

学校名称:深圳大学

队伍成员:倪家哲,贾东轩,邹泓高

指导老师:钟世达,张沛昌

优化思路

E203为了实现低功耗的要求,乘法器为基于booth编码和移位加法器结合的思路,优点是只需要一个加法器,而且该加法器还和除法器复用,可以说是将面积缩小到了极致。缺点也很明显,即使通过booth编码后部分积缩小为一半,仍有17个部分积,需要17个周期才能完成一次乘法指令(也不能说是缺点,只是为了减小资源消耗所做出的妥协。说实话,这个乘法器的代码写的很漂亮,我都不想改)。

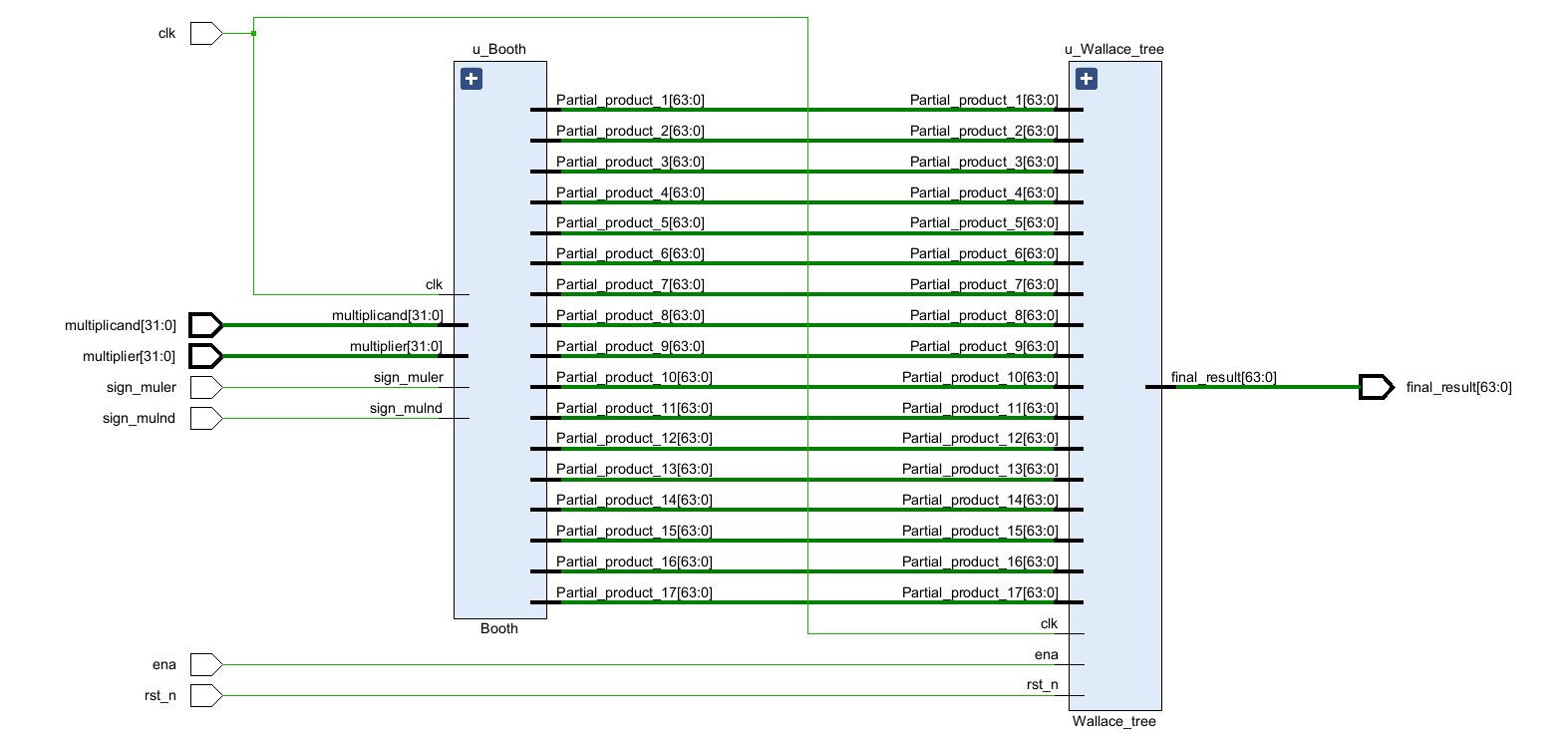

修改后的乘法器将booth编码与wallace树算法相结合,电路框图如下:

booth编码模块生成部分积,将部分积送入wallce模块中进行压缩计算,算出最终的乘法结果,将一个乘法指令缩减到2个周期(1th:rs1和rs2寄存器输入乘法操作数,乘法器进行乘法操作,2th输出乘法结果)。

目前优化后的乘法器输出结果是64位的,后面会继续优化算法,改为32位的(减小资源消耗),根据乘法指令的不同选择输出低32位还是高32位。

跑分结果

在基于vcs+verdi联合仿真没有问题之后,将代码下载进FPGA进行跑分测试,通过NucleiStudio烧写程序并通过串口打印到屏幕。

开发板:ALINX 7103

开发环境:vivado2021.2+NucleiStudio2022.08

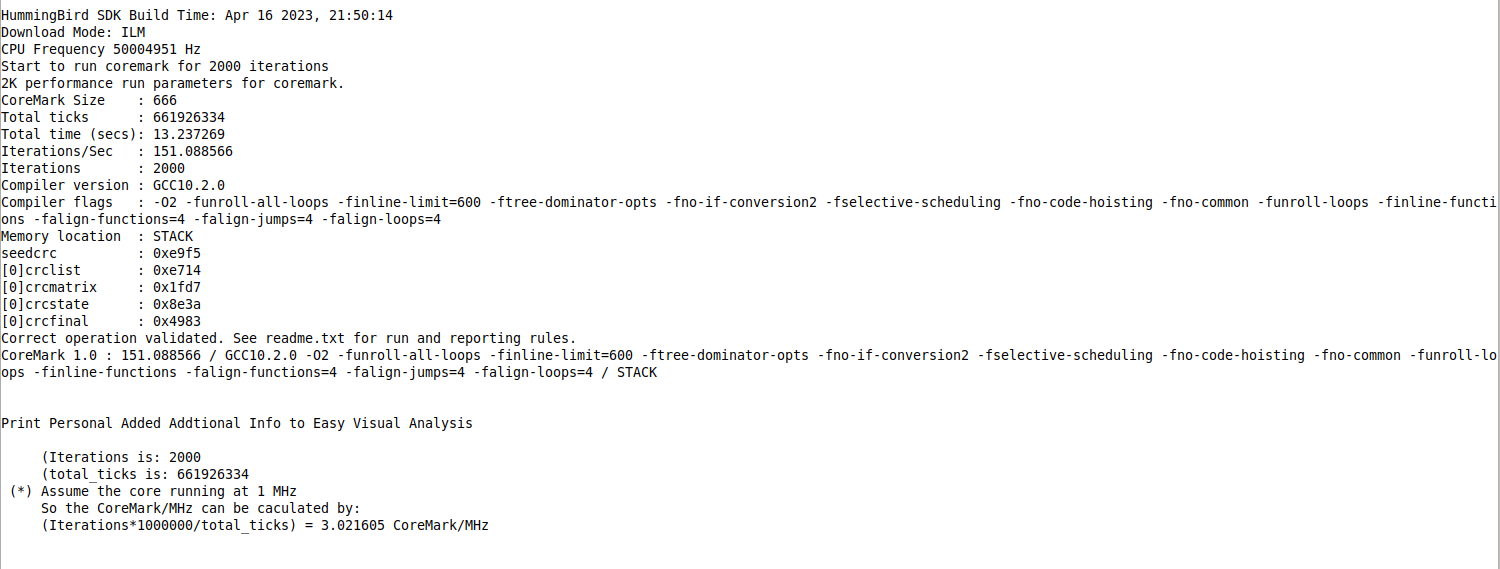

coremark跑分

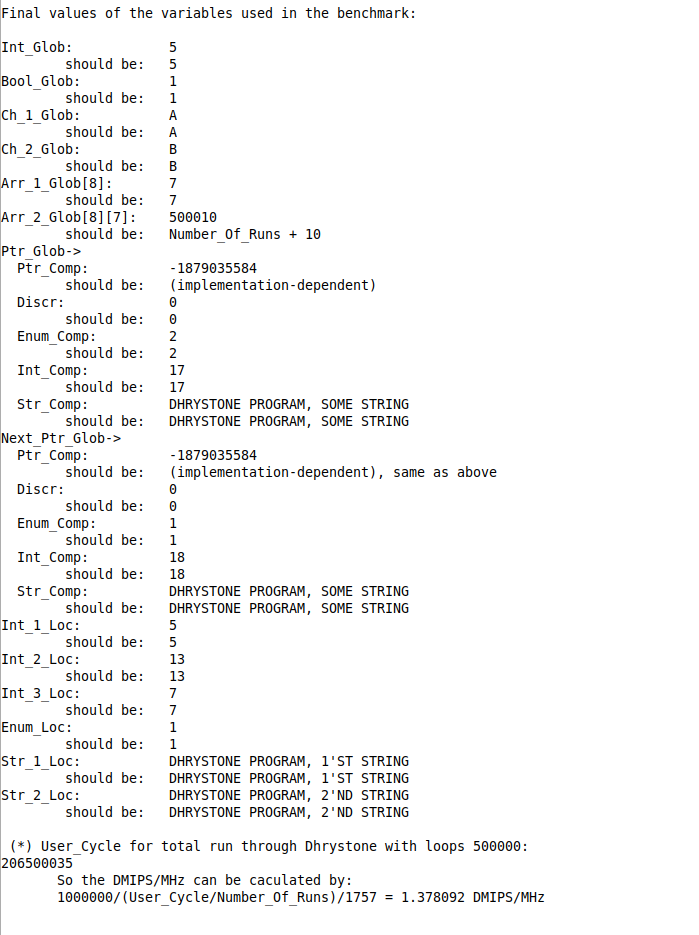

dhrystone跑分

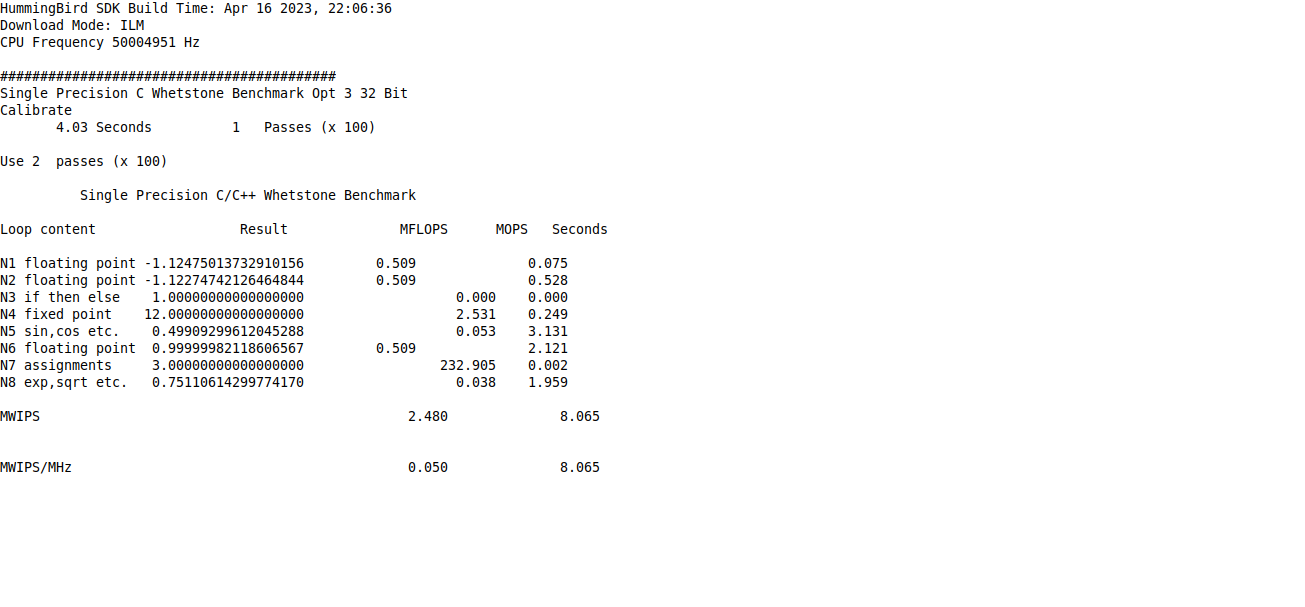

whetstone跑分

可以看到,优化乘法器对于提升跑分有着很大作用。