报名编号:CICC2469

团队名称:AM

学校名称:广东工业大学

队伍成员:林贤、刘合明、谢泽铭

指导老师:郑欣、高怀恩

环境:Vivado2021.1、NucleiStudio_IDE_202102-win64

内容:简单讲解下利用vivado来调用控制模块,以实现ov7725摄像头的视频数据流传输。

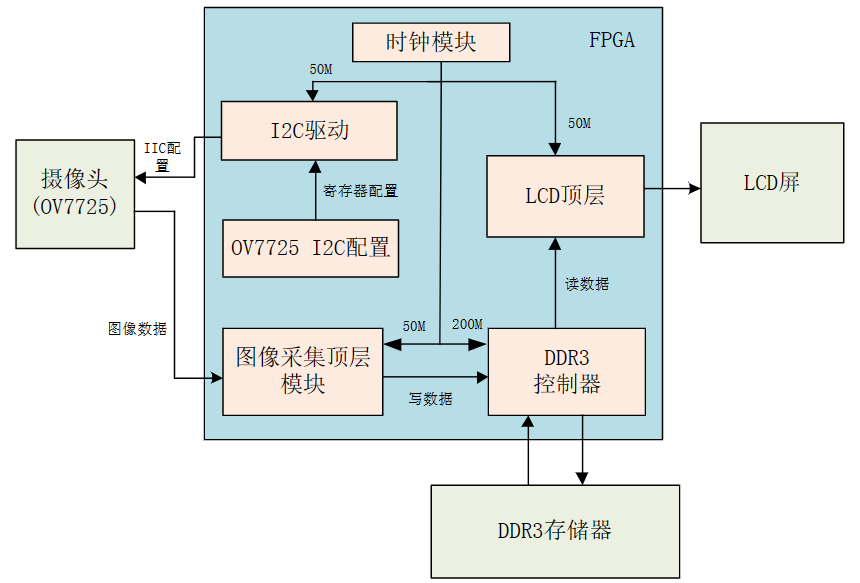

首先设计顶层的数据流传输模块总框架如下图所示:

这里FPGA板子上会有几个顶层模块,分别是:时钟模块为 LCD 顶层模块、DDR 控制模块以及 I2C 驱动模块提供驱动时钟。I2C 配置模块和 I2C 驱动模块控制着传感器初始化的开始与结束,传感器初始化完成后图像采集模块将采集到的数据写入 DDR 控制模块,LCD 顶层模块从 DDR 控制模块中读出数据,完成了数据的采集、缓存与显示。需要注意的是图像数据采集模块是在 DDR3 和传感器都初始化完成之后才开始输出数据的,避免了在 DDR3 初始化过程中向里面写入数据。

为了避免当前读取的图像与上一次存入的图像存在交错这一情况,我们在 DDR 的其它 BANK 中开辟一个相同大小的存储空间,使用乒乓操作的方式来写入和读取数据。

图像数据总是在两个存储空间之间不断切换写入,而读请求信号在读完当前存储空间后判断哪个存储空间没有被写入, 然后去读取没有被写入的存储空间,读取的速度远远大于写入的速度,虽然这样处理会比较慢,但是保证了读取的图片是完整的一帧,保证了不会出现帧交错的情况。是否进行乒乓操作的判断代码如下所示:

//将数据读写地址赋给ddr地址

always @(*) begin

if(~rst_n)

app_addr <= 0;

else if(state_cnt == READ )

if(ddr3_pingpang_en)

app_addr <= {2'b0,raddr_page,app_addr_rd[24:0]};

else

app_addr <= {3'b0,app_addr_rd[24:0]};

else if(ddr3_pingpang_en)

app_addr <= {2'b0,waddr_page,app_addr_wr[24:0]};

else

app_addr <= {3'b0,app_addr_wr[24:0]};

end

代码表示的意义是:当乒乓使能为高时,对读写存储空间进行乒乓操作,保证读写的存储不会在同一个空间,反之,就不进行乒乓操作,使读写的存储在同一个空间。

具体的顶层调用如上面所述,同时,在数据处理方面要注意:输入DDR3顶层模块的数据和DDR3顶层模块输出的数据都为16bit,而MIG的数据位宽为128bit,需要进行数据处理。