报名编号:CICC1764

团队名称: 两年半IC练习生

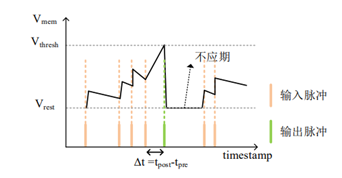

如图所示展示了LIF神经元的膜电势Vmem随时间戳timestamp动态变化的过程,当接收到输入脉冲后,LIF神经元的膜电势值Vmem便会升高,直至达到阈值电压Vthersh,此时神经元产生输出脉冲,这个过程被形象的叫做“积分点火”,释放输出后,Vmem便立刻变为Vrest。然后进入不应期,在不应期内无论是否接收到输入脉冲,其膜电势都保持静息电位。此外在一段时间内若没有接收到输入脉冲,膜电势也会发生泄漏而降低。

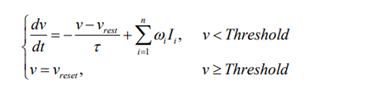

以下公式 用来计算LIF模型的膜电势

其中表示神经元的膜电势,vrest 代表神经元复位电位,为时间常数。是权重和输入脉冲的乘累加,结果再与膜电势相加。当神经元接收到输入脉冲时,I_i等于1,否则 I_i等于0。当膜电位超过阈值,神经元发出脉冲,然后膜电位变为静息电位vrest,并且膜电位在一段时间内不允许改变时间,称为不应期。如果膜电位没有超过阈值,膜电位呈指数衰减直到为静息电位 vrest。

LIF神经元模型在生物可解释性上低于其他模型,只体现了神经元计算的关键特性,并不能够解释真实神经元的脉冲是如何生成,也不包括丰富的神经元行为特性。但由于其简单的操作量更适合硬件实现。所以现有的大部分 SNN 加速器的硬件实现上都采用LIF模型。

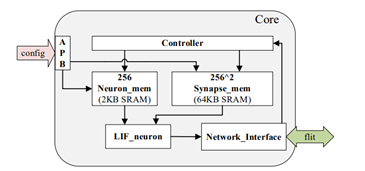

如图所示,设计的 SNN 神经核整体架构如图所示。

神经核主要由 LIF 神经元模块(LIF_neuron)、控制模块(Controller),神经元状态存储模块(Neuron_mem)和突触存储模块(Synapse_mem),神经元状态更新模块(LIF_neuron),神经核接口模块(Network_interface)组成;其中配置信息通过 APB 接口配置到神经元状态存储模块和突触存储模块,对神 经核使用的神经元模型参数,突触权重,神经元个数等参数进行初始化。控制模块负责安排神经元状态更新模块的计算,生成地址和控制信号;LIF 神经元模块是模拟神经元行为的关键模块;每个神经核包括两个存储模块,其中神经元状态存储模块存储 逻辑神经元的状态参数,包括膜电位、神经元时间参数等信息,突触存储模块存储权重,每个物理神经元都有自己的存储单元,位于 LIF 神经元模块旁边。这种分布式的SRAM实现了近似存算一体的架构,解决了传统的冯诺依曼结构带来的瓶颈,减少了数据的远距离搬运;神经核接口模块主要负责完成脉冲数据包和数据微片两种数据格式之间的相互转换。

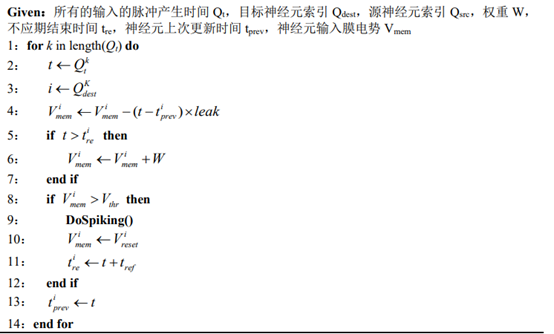

在膜电势的计算微分方程基础上,对模型进行优化,如下述伪代码所示描述了采用事件驱动方式的 LIF 计算模型: