队伍编号:CICC3454 喝可乐队

SD卡读写控制,Xilinx官方并没有提供相关的IP,故本项目自主设计并封装为可复用IP核。

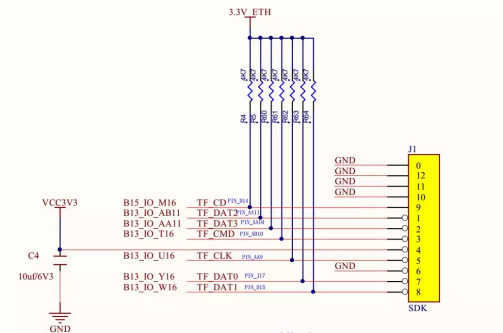

根据Micro SD卡的引脚图,其可工作在SDIO模式或者SPI模式。在SDIO模式下,共用到CLK、CMD、DAT[3:0]六根信号线;在SPI模式下,共用到CS(SDIO_DAT[3])、CLK(SDIO_CLK)、MISO(SDIO_DAT[0])、MOSI(SDIO_CMD)四根信号线。在本工程中,SD卡工作在SDIO模式下。

SD卡的写操作流程如下:

s_axi_rdata <= 0;

s_axi_rresp <= 0;

s_axi_rvalid <= 0;

s_axi_bresp <= 0;

s_axi_bvalid <= 0;

rd_req <= 0;

wr_req <= 0;

read_addr <= 0;

write_addr <= 0;

write_data <= 0;

cmd_start <= 0;

data_int_rst <= 0;

cmd_int_rst <= 0;

ctrl_rst <= 0;

argument_reg <= 0;

command_reg <= 0;

cmd_timeout_reg <= 0;

data_timeout_reg <= 0;

block_size_reg <= `RESET_BLOCK_SIZE;

controller_setting_reg <= 0;

cmd_int_enable_reg <= 0;

data_int_enable_reg <= 0;

software_reset_reg <= 0;

clock_divider_reg <= `RESET_CLOCK_DIV;

block_count_reg <= 0;

sd_insert_ie <= 0;

sd_remove_ie <= 0;

dma_addr_reg <= 0;

if (clock_posedge) begin

cmd_start <= 0;

data_int_rst <= 0;

cmd_int_rst <= 0;

ctrl_rst <= software_reset_reg[0];

end

if (s_axi_arready && s_axi_arvalid) begin

read_addr <= s_axi_araddr;

rd_req <= 1;

end

if (s_axi_rvalid && s_axi_rready) begin

s_axi_rvalid <= 0;

end else if (!s_axi_rvalid && rd_req) begin

s_axi_rdata <= 0;

if (read_addr[15:8] == 0) begin

case (read_addr[7:0])

`argument : s_axi_rdata <= argument_reg;

`command : s_axi_rdata <= command_reg;

`resp0 : s_axi_rdata <= response_0_reg;

`resp1 : s_axi_rdata <= response_1_reg;

`resp2 : s_axi_rdata <= response_2_reg;

`resp3 : s_axi_rdata <= response_3_reg;

`controller : s_axi_rdata <= controller_setting_reg;

`blksize : s_axi_rdata <= block_size_reg;

`voltage : s_axi_rdata <= voltage_controll_reg;

`capa : s_axi_rdata <= capabilies_reg;

`clock_d : s_axi_rdata <= clock_divider_reg;

`reset : s_axi_rdata <= { cmd_start, data_int_rst, cmd_int_rst, ctrl_rst };

`cmd_timeout : s_axi_rdata <= cmd_timeout_reg;

`data_timeout : s_axi_rdata <= data_timeout_reg;

`cmd_isr : s_axi_rdata <= cmd_int_status_reg;

`cmd_iser : s_axi_rdata <= cmd_int_enable_reg;

`data_isr : s_axi_rdata <= data_int_status_reg;

`data_iser : s_axi_rdata <= data_int_enable_reg;

`blkcnt : s_axi_rdata <= block_count_reg;

`card_detect : s_axi_rdata <= { sd_remove_int, sd_remove_ie, sd_insert_int, sd_insert_ie };

`dst_src_addr : s_axi_rdata <= dma_addr_reg;

endcase

end

s_axi_rresp <= 0;

s_axi_rvalid <= 1;

rd_req <= 0;

end

if (s_axi_awready && s_axi_awvalid) begin

write_addr <= s_axi_awaddr;

wr_req[0] <= 1;

end

if (s_axi_wready && s_axi_wvalid) begin

write_data <= s_axi_wdata;

wr_req[1] <= 1;

end

if (s_axi_bvalid && s_axi_bready) begin

s_axi_bvalid <= 0;

end else if (!s_axi_bvalid && wr_req == 2'b11) begin

if (write_addr[15:8] == 0) begin

case (write_addr[7:0])

`argument : begin argument_reg <= write_data; cmd_start <= 1; end

`command : command_reg <= write_data;

`reset : software_reset_reg <= write_data;

`cmd_timeout : cmd_timeout_reg <= write_data;

`data_timeout : data_timeout_reg <= write_data;

`blksize : block_size_reg <= write_data;

`controller : controller_setting_reg <= write_data;

`cmd_isr : cmd_int_rst <= 1;

`cmd_iser : cmd_int_enable_reg <= write_data;

`clock_d : clock_divider_reg <= write_data;

`data_isr : data_int_rst <= 1;

`data_iser : data_int_enable_reg <= write_data;

`blkcnt : block_count_reg <= write_data;

`card_detect : begin sd_remove_ie <= write_data[2]; sd_insert_ie <= write_data[0]; end

`dst_src_addr : dma_addr_reg <= write_data;

endcase

end

s_axi_bresp <= 0;

s_axi_bvalid <= 1;

wr_req <= 0;

end

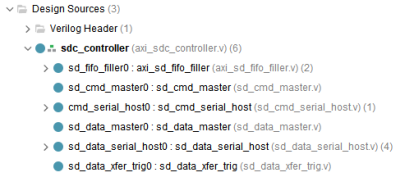

将其与FIFO封装为IP,IP核包括的文件结构如下:

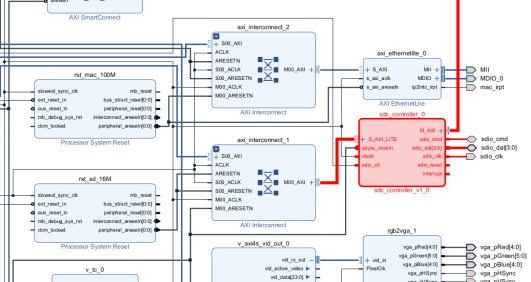

通过AXI总线,将SD卡控制器挂载在SoC上,通过中央处理器进行配置与控制,并引出SDIO_CMD、DAT[3:0]与CLK引脚,通过SoC顶层system文件引出。

在xdc文件中绑定引脚如下:

set_property PACKAGE_PIN AB15 [get_ports {sdio_dat[3]}]

set_property PACKAGE_PIN AA15 [get_ports {sdio_dat[2]}]

set_property PACKAGE_PIN AB17 [get_ports {sdio_dat[1]}]

set_property PACKAGE_PIN Y16 [get_ports {sdio_dat[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sdio_dat[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sdio_dat[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sdio_dat[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sdio_dat[0]}]

set_property PACKAGE_PIN W14 [get_ports sdio_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sdio_clk]

set_property PACKAGE_PIN Y14 [get_ports sdio_cmd]

set_property IOSTANDARD LVCMOS33 [get_ports sdio_cmd]

set_property PACKAGE_PIN AA16 [get_ports sdio_cd]

set_property IOSTANDARD LVCMOS33 [get_ports sdio_cd]

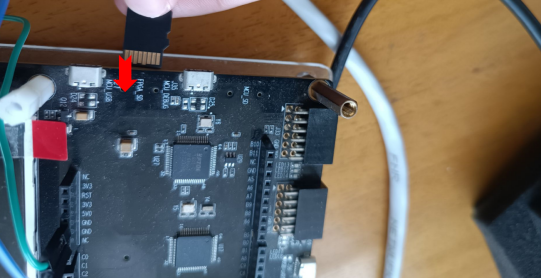

将32GB的Micro SD卡通过Windows/Linux下的磁盘管理工具进行格式化,并添加卷为FAT32,接入开发板时选择开发板上标注FPGA_SD的SD卡接口,通过软件控制读写,具体软件驱动见后续分享。