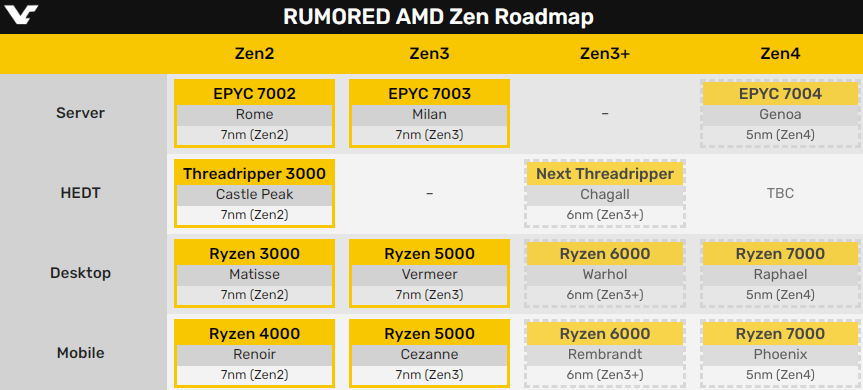

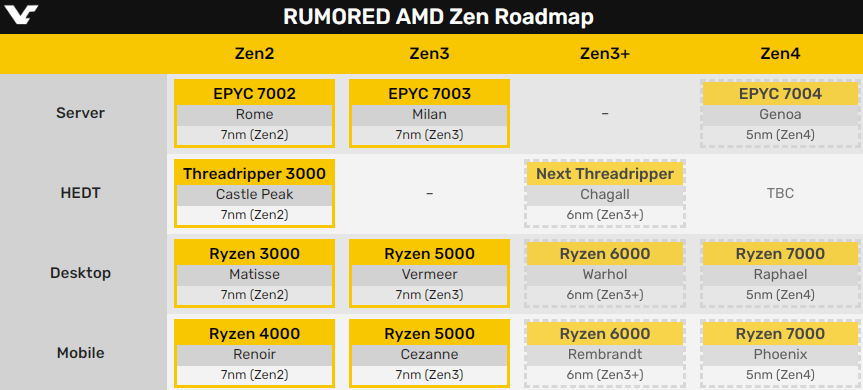

AMD Zen家族的未来似乎存在诸多变数,比我们预期得要慢不少。曾经踩爆Intel牙膏,但种种因素之下,AMD自己却有了一些“挤牙膏”的嫌疑。根据早先传闻,AMD下一步将推出过渡性质的Zen3+架构的“Warhol”(沃霍尔),6nm工艺,但最新说法是它已经取消,改为升级版的Zen3 XT或者叫Zen3 Refresh,类似锐龙3000XT系列,但依然命名为锐龙6000系列。

根据最新曝料,Zen4架构的“Raphael”(拉斐尔)要到2022年9-10月份才会宣布,10-11月份上市,也就是距离Zen3架构的锐龙5000系列足足两年之久。另一方面,Intel将在年底推出AlderLake 12代酷睿,首次桌面10nm工艺,首次大小核架构,首次DDR5内存——难道,AMD认为面对这一代,Zen3就已经足矣?Intel明年还有升级版的RaptorLake 13代酷睿,它才会真正面对Zen4。根据目前掌握的情报,Zen4将会采用台积电5nm工艺制造,IPC性能提升超过20%,首次支持DDR5内存、PCIe 5.0总线,接口因此首次改为AM5,命名则是锐龙7000系列,各个平台的核心数量、APU集显性能都已经差不多定下来了。AMD官方路线图上,Zen4架构对应时间轴也比较模糊,反正最迟是2022年,AMD早就留了一手。

再往后的Zen5,传闻会是一次巨变,台积电3nm工艺,首次引入大小核架构,内存子系统也会有较大变化,预计2024年诞生,又是两年……据推特用户@KittyYYuko的消息,下一代Navi 33核心将具有目前旗舰级Navi 21核心同样的规格,如果情况属实,意味着拥有80个CU计算单元,以及5120个流处理器,同时采用新的RDNA 3架构。根据此前的爆料,Navi 31核心会采用MCM多芯片封装,也就是说Navi 31核心会拥有两个chiplet,双80个CU计算单元的设计,达到160个CU计算单元、10240个流处理器的规格。另外Navi 31和Navi 33之间的Navi 32核心,也将采用MCM多芯片封装,预计会有120-140个CU计算单元。另外Navi3x核心很可能会采用台积电(TSMC)的新工艺节点制造,比如5nm工艺。此前,AMD已经为其下一代GPU申请了一项新专利,是一颗有源小芯片,集成了高速缓存,用于多个GPU之间的桥接,可能会用在使用下一代RDNA 3架构的GPU和APU上。AMD的这颗主动式桥接芯片主要用于GPU芯片之间的高带宽互联,会拥有一个共享、统一的最后一级缓存(LLC),将提供跨芯片间通信的同步信号。LLC指的是L3缓存,在目前RDNA 2架构中,L3缓存被称为Infinity Cache(无限缓存)。根据AMD的规划,新一代的RadeonRX系列显卡要到2022年底或2023年初才亮相,对手是同样采用MCM多芯片封装技术的英伟达GPU,比如传闻中的Lovelace架构产品。不过近期业界一系列供应短缺可能会影响到各个厂商发布新品,此前推特用户@kopite7kimi曾表示,英伟达Ampere架构产品的寿命可能会延续到明年年底。