队伍编号: CICC3454

队伍名称: 喝可乐队

本项目在VPU部分添加了一个应用于嵌入式的轻量级向量协处理器,实现了部分的V型计算功能,满足本情景下的使用要求。VPU和CPU之间有五个接口的数据交互,交互有握手的协议进行控制。接口分别为:事务接口,处理结果接口,提交接口,内存请求接口与内存结果接口。其中,在请求接口CPU向VPU提供执行需要的指令、操作数和一些控制信息(例如操作数是否生效,指令标识等);在处理结果接口VPU返回操作结果;在提交接口CPU向VPU指出是否需要冲刷;在内存请求接口VPU发出内存请求数据包以访问内存并通过内存结果接口返回所需数据。

CPU在接受到指令后会在前端进行预解码,若解码结果为向量运算指令,会将信号传递给派遣单元和寄存器模组,派遣单元会将在OITF中为该向量指令完成注册(所有V指令均视为长指令),并将其发送至ALU中的VPU控制模块,其将指令和寄存器模组准备好的操作数传递给VPU。VPU接受到指令和数据开始行使功能,在结束完操作后返回数据给CPU,CPU在OITF上对向量指令进行解注册,并且将结果写回到寄存器组以及将执行情况反馈到提交模块。以下将对向量处理器中的各个模块进行详细介绍。

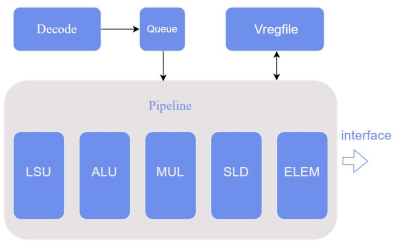

解码模块

解码模块将传入VPU的指令进行解码,同时判断是由哪一个运算单元进行运算。解码后的指令将被放入队列依序执行,通过Pipe模块发送到所对应运算单元。

队列模块

队列模块存储发往VPU的指令并按序将其发送至运算单元。当流水需要停顿时,队列模块会停止下一个指令的发送。

发送模块

发送模块经过逻辑判断,将CPU发来的运算数据和生成的控制信息发往运算单元

访存模块

向量访存模块集成出访存请求并由内存请求接口发送给CPU,通过CPU的访存模块访问内存。向量访存模块支持三种访存模式,连续访存,按步长访存和按索引访存。

连续访存,将根据首地址和突发长度信息生成一系列连续地址以访问一个连续的内存区;

按固定步长跳跃访存,将根据首地址和突发长度生成一个等差的地址数列来访问内存区,进行间隔性地访存。

按索引访存,根据一个向量中提供的多个地址偏移量生成索引地址,实现不规则的数据访存

由于通过CPU的访存模块进行读写操作,所以需要在蜂鸟核中增加相应的控制模块,将访存总线增加一个通道的宽度,并给予VPU最高的仲裁优先级。

另外访存模块会向外界发出工作状态信号,向其他模块示意是否有读写任务区正在进行,同时检测向量寄存器组传来的工作状态信息,若后者处于忙碌状态访存模块将会停止发送写回请求。

计算模块

通过解码,不同的V型运算会进入不同的运算模块。

寄存器模块

寄存器模块给出了三种可配置选项,使用普通寄存器组,使用Linux给出的RAM32M和ASIC模式。其中所使用的为普通模式,生成一个三读口一写口,深度为VREG_W所定义的32位寄存器组。

接口模块

在协处理器的顶层模块中,将计算结果以及控制信号集成到接口单元中,由于Vicuna核使用Systemverilog书写,其还需经过一个转接模块生成Verilog格式来接入蜂鸟核。

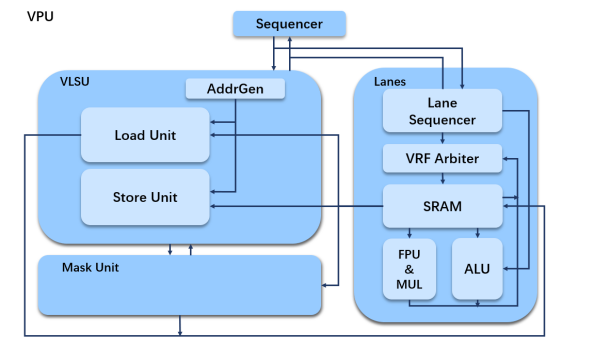

二、另外,我们还设置了可配置的VPU选项。以支持所有向量运算的开源处理器ARA为基础修改

指令序列模块

指令序列模块记录了正在VPU中正在执行的指令。

访存模块

向量访存模块直接对接AXI总线,直接访问DDR,由三个模块组成:地址发生器,存取模块和总线对接模块。向量访存模块支持三种访存模式,连续访存,按步长访存和按索引访存。当向量指令到来时,其中的状态机将根据操作条件跳转。

寄存器模块

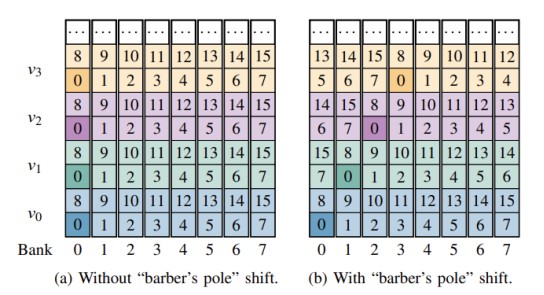

寄存器模块分为8个bank,每个bank都是单端口读写的,读出的数据会进入操作数队列以供给执行模块。向量数据在Bank中的排布采用了barber’s pole的偏移排布方式,如图所示,将向量的首项规律地向后偏移一位,以免在读取数据时产生冲突(对于向量计算总是会先取两个向量的首项开始计算,为了减小硬件开销bank是单端口读写的,通过这样精妙的重排技术能够让两个bank同时工作去取出数据进行计算而不会因为读同一bank而造成堵塞)

浮点模块

相关的V型浮点运算结合了V型指令的控制方式FPU中的浮点计算方法。

三、 我们将VPU挂载在CPU内核外,提高整体可重构性。配置了VPU以后,对一些模型有了明显的加速效果。